LCoS显示芯片的研制

摘要: 介绍LCoS显示芯片的研制。三片式投影用LCoS显示芯片的物理结构及其电路组成框图;芯片整体设计方法,运用Cadence EDA工具设计LCoS显示芯片的具体策略和相应步骤;给出了LCoS显示芯片的实际设计结果,并对其光学参数进行了测量。

本文引用地址:https://www.eepw.com.cn/article/88060.htm关键词: 硅基液晶 全定制设计 自顶向下 工艺文件

LCoS(硅基液晶)作为新型显示器件,具有大屏幕、高亮度、高分辨率、省电等诸多优势,用LCoS技术制作高分辨率光阀的方法逐渐在平板显示界占有一席之地[1]。本文设计的用于三片式彩色投影机的高集成化LCoS显示芯片,采用标准0.6μm-四层金属-双电源CMOS工艺设计和制作,其空间分辨率为800×600像素,目前已在国内半导体生产线上小批量成功流片。

1 LCoS显示器件的物理结构与性能

LCoS显示器是一种反射式光调制器,不影响入射光到每个像素的截面积,从而大大提高了开口率[2]。笔者设计的三片式投影显示系统采用空间混色法实现彩色化,即分别用三片LCoS芯片控制红绿蓝三基色图形,然后通过光学系统实现空间混色。

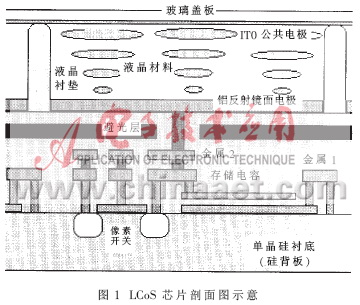

笔者采用标准0.6μm-n阱-四层金属CMOS工艺设计的单色LCoS器件物理结构剖面图如图1所示。图中,把金属3设计成避光层,金属4设计成反射镜面电极,其目的是使金属3和4交叠遮盖显示矩阵的有源部分,从而完全挡住了入射光线,降低了NM0S晶体管源极PN结上产生的光生漏电流。这种设计可防止因此而引起的图像对比度退化。

在芯片制作过程中采用了CMOS制造工艺中的整平技术,以确保硅片表面是光学平面。整平工艺使得LCoS硅芯片在像素内的局部平整度变化小于100A°,像素间的总体平整度变化小于500A°。采用这种整平工艺可使硅光阀的光学性能大大地改进[3]。这些改进包括三个方面:首先,平整的表面提高了像素的金属镜面质量,使得光学反射性增强;第二,在液晶盒的后阶段制造中,平整的表面改善了液晶的排列,使液晶盒的可靠性和特性变得更好;最后,在像素上镀了一层电介质镜面,进一步改善了金属的反射性能。

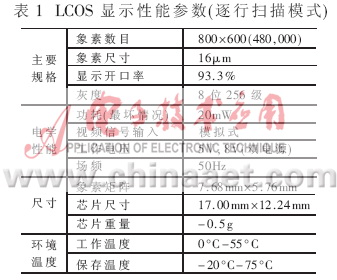

为了提高本次设计的成功率,采用投影显示系统中主流产品的显示性能指标(见表1)。这样,一方面不会因为芯片电路结构的复杂性,使得设计难度大幅度地增加,而转移本科研的注视点;另一方面,若这种模拟式单色显示方式能成功实现,可直接与主流产品接轨。

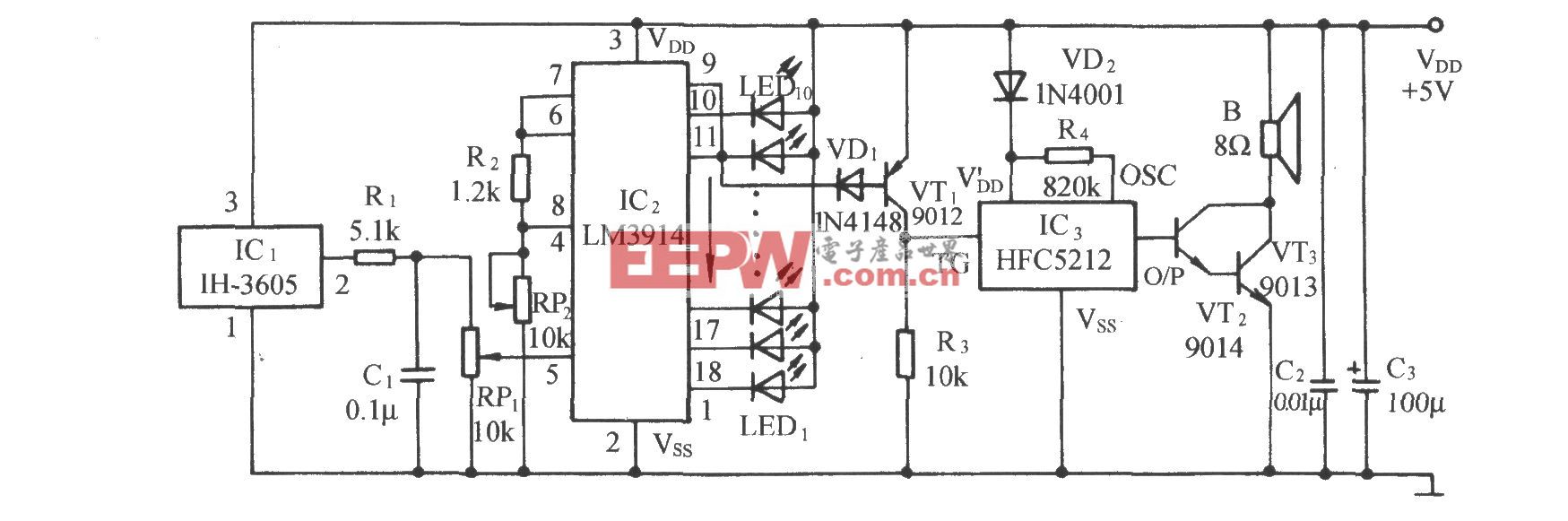

2 显示芯片电路系统

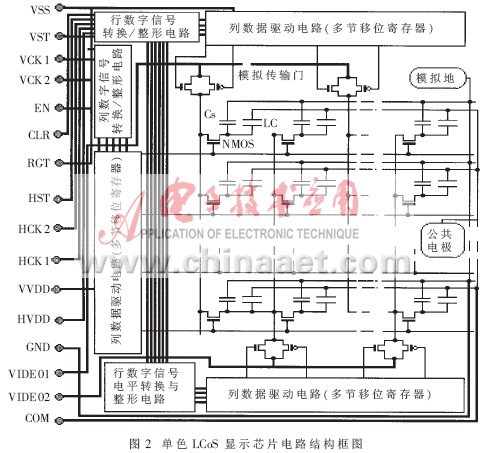

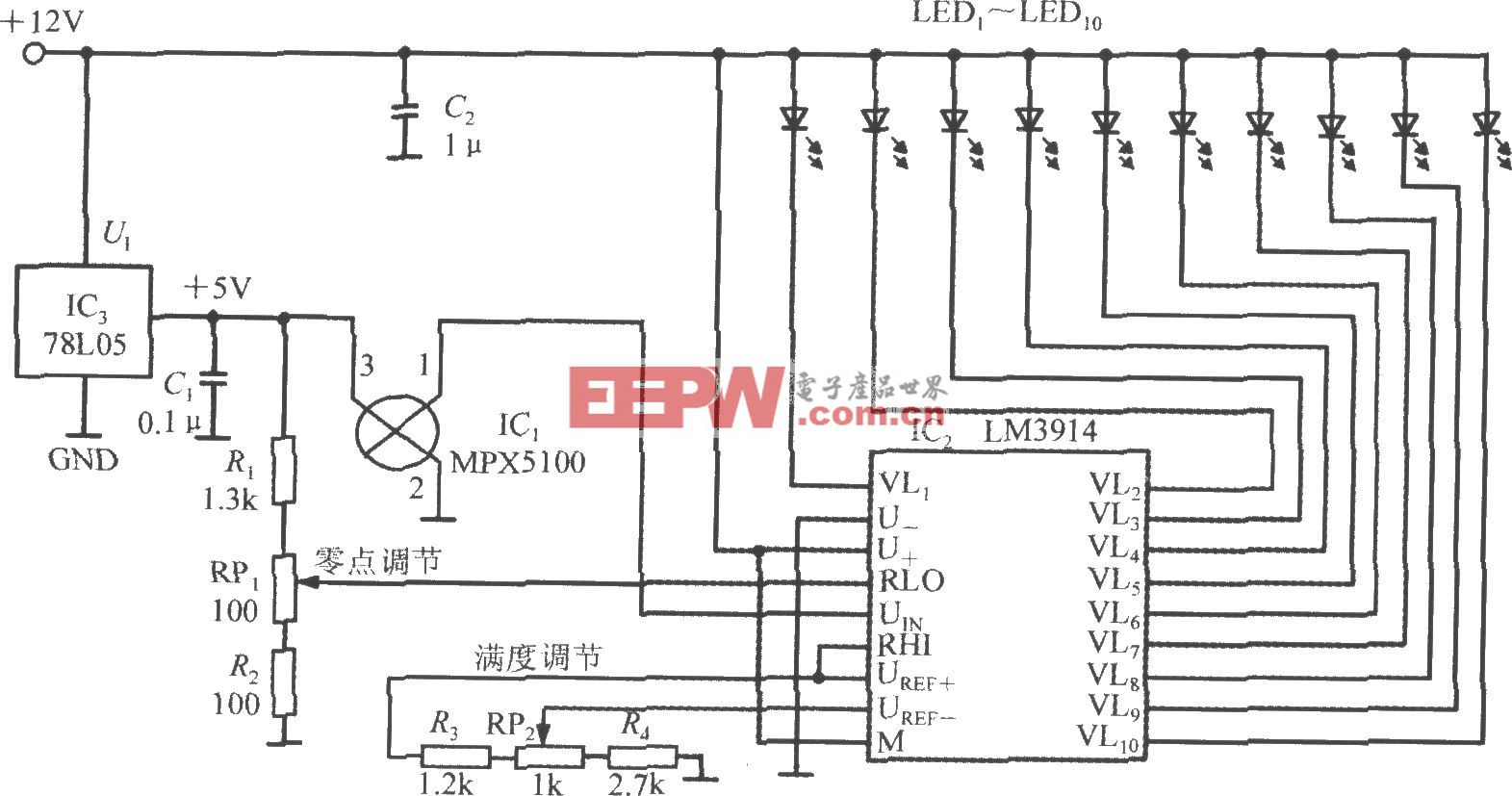

图2给出了LCoS芯片的电路结构框图。总体上芯片电路可划分为行扫描驱动器、列数据驱动器和显示像素矩阵。为了降低芯片工作频率,同时利于周边驱动电路布局布线,把列数据驱动器分成电学结构完全一致的上下两组,分别驱动奇偶数据线。

LCoS显示芯片采用逐点寻址方式,行扫描驱动器位于芯片左边,它有600个驱动单元,依照帧触发时钟脉冲VST和扫描时钟脉冲VCK1VCK2同步控制,从第一行到最后一行依次驱动。另一方面,上下列数据驱动器各由一个双向可选择的400节移位寄存器和一组模拟传输门组成。移位寄存器在信号时钟脉冲HST和像素时钟脉冲HCK1HCK2的控制下,从左到右依次将信号输入400个模拟传输门,控制其对视频模拟信号的导通时间。结果以恒定的间隔取样连续的单色视频图像信号,并直接输入到相应的视频信号电极线,从而作用到正被选取的扫描行的像素电极上。

单色LCoS芯片采用视频信号电极逐场反转模式,即作用在像素电极上的信号电平相对于上盖玻璃基片上公共电极的电压,每一帧都改变一次极性,于是视频信号成为周期性改变的交流电压,从而可以防止液晶材料的电化学退化。

3 采用EDA技术设计LCoS芯片

从前面的分析可以发现,LCoS芯片不可能直接采用标准单元、门阵列等半定制方法来实现。实际上,LCoS芯片的物理版图实属LSI级,其设计过程十分复杂,较好的设计策略是采用层次设计与EDA设计相结合的方法,基本的设计过程是采用自顶向下的设计。具体地说,使用具备全定制设计功能的Cadence EDA设计工具,按照“自顶向下”的规则来设计LCoS芯片的版图。首先确定微显芯片的功能、性能、允许的芯片面积和成本等;接着进行结构设计,分化出尽可能简单的子系统;然后把各子系统间的逻辑关系转换成电路图,进行电路逻辑设计和电路仿真;最后采用全定制方法综合出整个LCoS芯片版图。设计好的版图还要通过提取版图的结构信息和寄生参数信息与原来的结构描述相比较,验证它们之间的一致性。

3.1 数据准备

笔者采用具有4层金属布线的CMOS工艺路线来实现LCoS芯片。为此首先在Cadence环境下编写与Diva验证工具相匹配的工艺文件(LCoS.tf)[4]。其中包括:①LCoS芯片光刻版图层及其属性的定义;②符号元件;③DRC、ERC、LVS检查规则;④寄生电阻、电容提取规则;⑤抽象单元规则。

3.2 建立LCoS显示芯片的单元库

笔者为LCoS显示芯片建立的基本单元包括:反相器、门电路、准静态D触发器、模拟电子开关、基本运算放大器、电平变换器以及各种应用的I/O单元[5]。考虑到各基本单元的逻辑功能不同,其版图面积的大小也不可能一样,因此规定列方向上的基本单元,其宽度一致;而在行方向上的基本单元,其高度一致;并且与显示矩阵的规则排列相一致。这为整个版图的快速组合铺平了道路。

3.3 版图布局策略

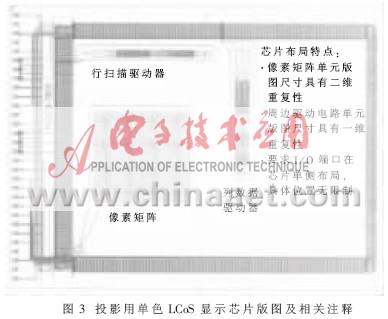

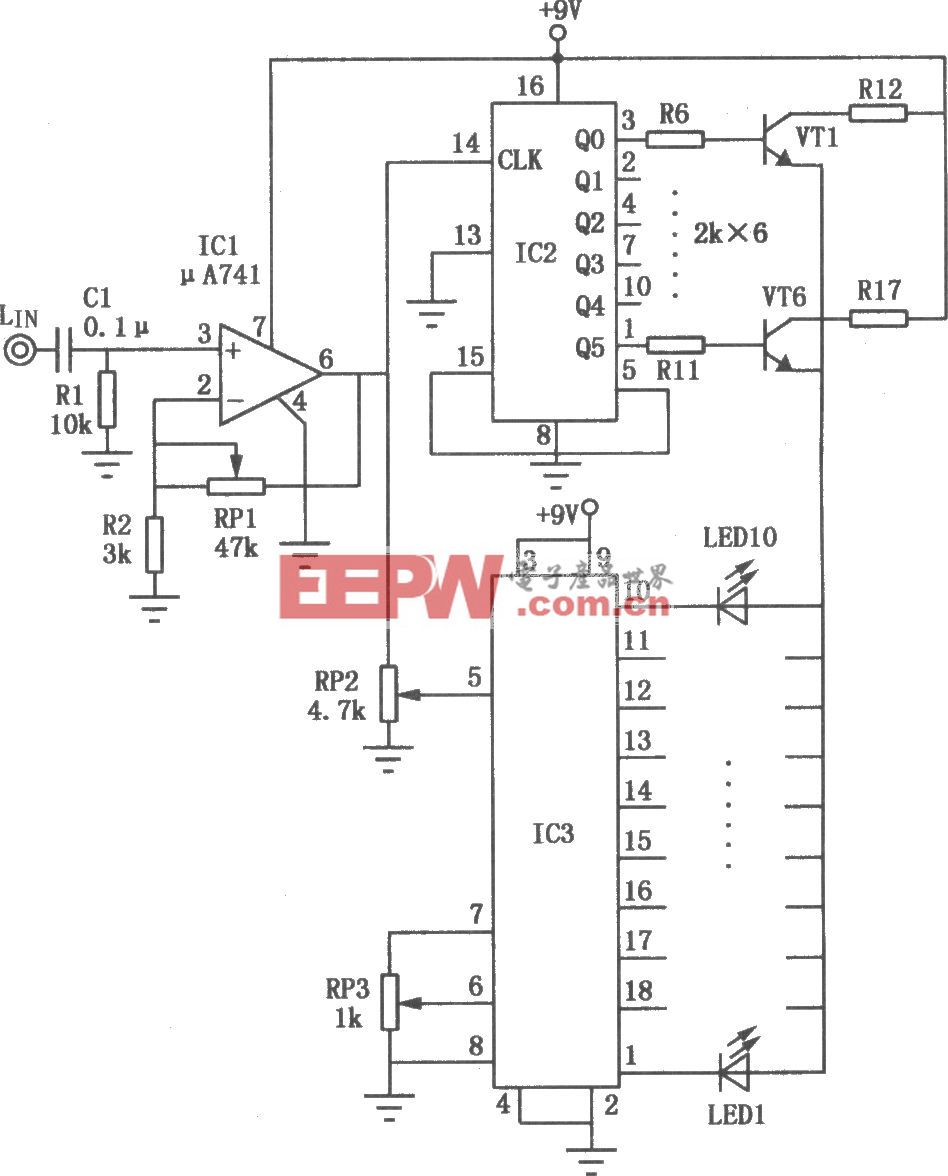

布局是指将模块安置在芯片上的适当位置,并能满足一定的目标函数。由于LCoS显示芯片在整体物理结构方面具有严格的横向或纵向对称性,可以免去那些在常规半导体版图设计中采用的顶层规划与底层规划。当运用LCoS显示芯片的单元物理视图完成单行或单列的版图优化时,可在Cadence平台上设置LCoS显示矩阵截距,然后反复复制单行或单列的物理视图来实现LCoS显示芯片的主要版图布局规划。图3是笔者在Cadence平台上规划出的LCoS(SVGA分辨率)显示芯片版图,图中像素截距设计为16μm,其芯片对角线保持在21mm(约0.83英寸)左右。

3.4 版图验证

版图验证的任务是检查版图中可能存在的错误。因此,在完成LCoS显示芯片布局、布线后,笔者在Cadence平台上进行了版图验证,包括设计规则检查、电学规则检查以及版图与电路图的一致性检查,并在版图寄生参数提取的基础上再次进行电路分析(即后仿真)。在所有的检查都通过并被证明正确无误后,将布图结果转换为掩膜文件。然后由掩膜文件设法生成掩膜版,通常这可通过掩膜版发生器或电子束制版系统得到。

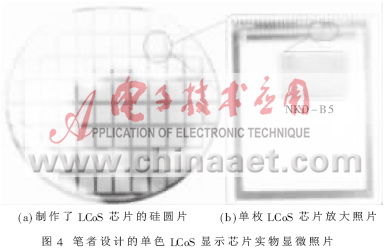

4 芯片实物显微图片

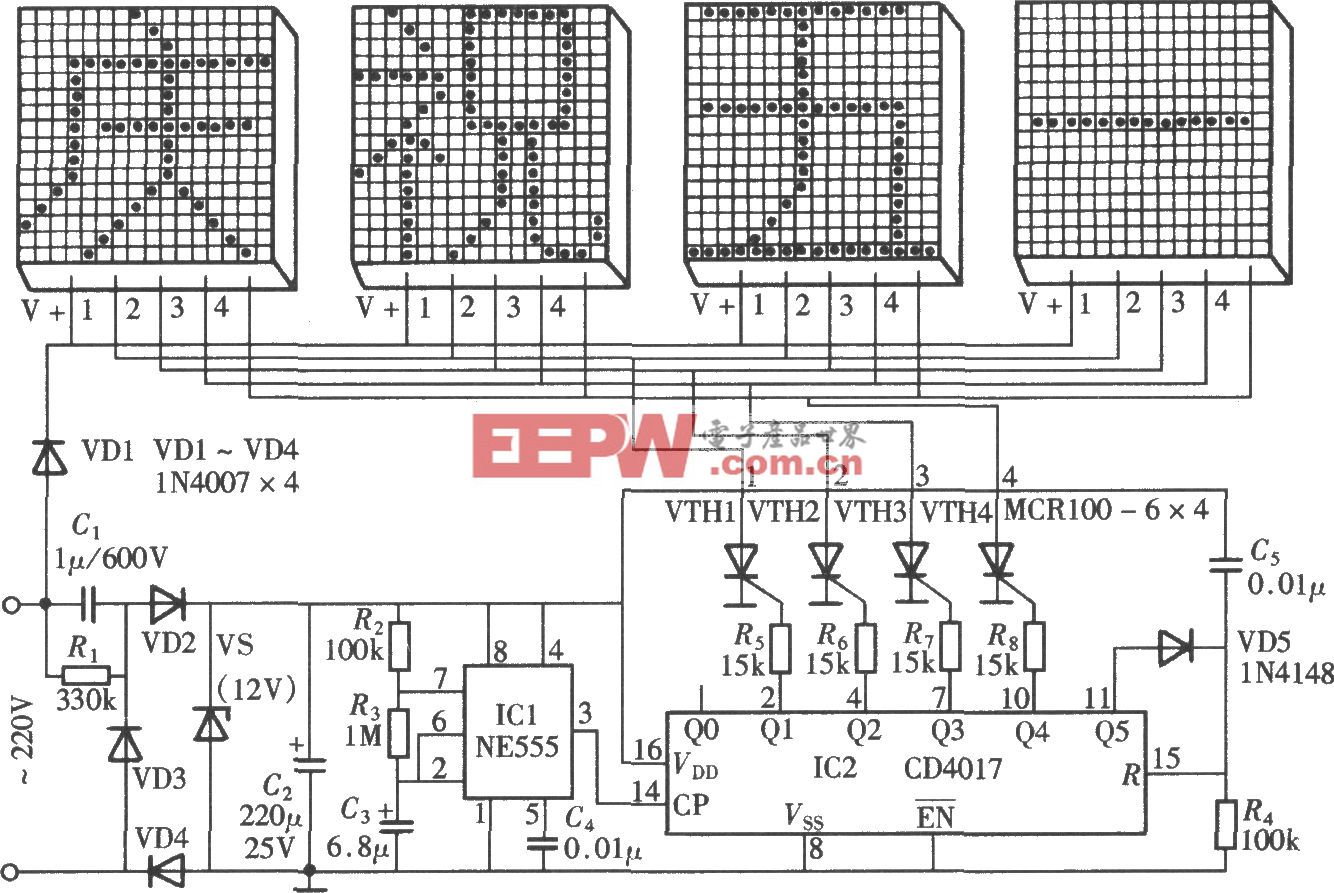

图4给出了研制的投影用单色LCoS显示芯片实物显微照片。这是采用国内某半导体生产线0.6μm-CMOS工艺在6英寸硅片上制作的,每枚芯片尺寸为17010μm×12420μm,其中显示矩阵尺寸为12800μm×9600μm,即对角线尺寸约为0.63英寸。在每片6英寸硅圆片的有效平面光刻范围内可制作60枚LCoS显示芯片。图4(b)是单枚LCoS显示芯片显微放大照片,其中特意放大了芯片名称:NKD-B5,以示该显示芯片为国内自主研制生产,具有中国的自主知识产权。

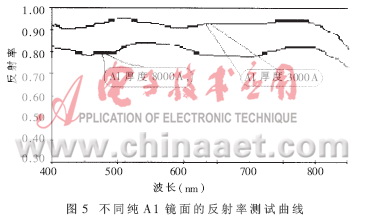

5 镜面电极光学性能测试结果

作为反射式调制光阀的LCoS显示器,其光通量是一个关键参数,而光通量依赖于像素电极反射镜面的尺寸、镜面的反射率及其平整度。在显示面积一定的情况下,像素电极反射镜面的尺寸直接与像素的开口率成线性关系。本文研制的LCoS芯片的像素截距是16μm,像素间距是0.54μm,可得到的像素开口率:

![]()

图5是不同厚度纯Al(99.999%)薄膜的反射率测试结果,表明了纯Al镜面的反射率受其薄膜厚度的影响。实际上,纯Al膜如果沉积较厚(1μm以上)容易形成“铝丘”[6],即出现多晶态的Al分布,一方面使Al膜表面粗糙,降低其镜面反射率,另一方面将严重影响Al膜的电学性能。因此,根据上述实验结果,本篇论文采用3000.厚的纯Al膜制作LCoS显示芯片的镜面反射电极。

目前LCoS的发展业者集中在美英两地的Fabless公司[7],国内在LCoS投影机光学引擎、光源、整机设计及LCoS设计以及液晶板制造方面均有研发和向产业化方向转移的趋势。更令人振奋的是,我国在向LCoS技术领域的进军中,并没有停留在低技术含量的系统组装范畴。以南开大学等一批高等院校、科研机构为先驱,在不同渠道资金的支持下,奋先展开了研发具有中国自主知识产权(IP)的LCoS显示芯片[8]。可以预见,在中国以LCoS技术为核心的新型平板显示产业即将兴起。

参考文献

1 Robert L.Melcher. LCoS-Microdisplay Technology and Applications. Information Display, 2000; 16(7): 20~23

2 Morrissy J.H,Pfeiffer M, Schott D, Vithana H. Reflective Microdisplays for Projection or Virtual-View Applications.SID'99 Digest, 1999; 30(6): 180~183

3 H.C.Huang, D.D.Huang, J.Chen. Optical Modeling of Small Pixels in Reflective Mixed Mode Twisted Nematic Cells, SID’ 99Digst, 1999, 30(1): 18~22

4 Chip Assembly Design Flow Guide. CADENCE Inc., December 1994

5 代永平, 孙钟林, 耿卫东. 彩色LCoS微型显示器设计.半导体技术, 2001; 26(10): 37~39

6 Cacharelis P,Kim U,Frazee J,Moore P,Brown K,Littrell R,Renteln P,Flack R. An 0.8 micron EEPROM Technology Modified for a Reflective PDLC Light-Valve Application.Boston: SID International Symposium Digest of Technical(Papers XXVIII), 1997: 289~292

7 Chris Chinnock. Microdisplays and Manufacturing Infrastructure Mature at SID2000. Information Display, 2000;16(9):18~21

8 Dai Yongping, Gen Weidong, Sun Zhonglin.Optimizing the Design for Microdisplay on Silicon, Creating IP Modules for a New Type of SOC. ShangHai: 2001 4th International Conference On ASIC Proceedings, 2001:785~788

评论