基于SOPC的视频采集系统设计

在FPGA上实现嵌入式系统,主要是构建片内MicroBlaze处理器,并为处理器添加片内外设以实现硬件模块功能,同时应添加片内外设与芯片外部引脚的连接。在开发片内外设的同时,应开发外设功能的底层驱动程序,然后在MicroBlaze处理器上实现系统应用程序。这是个软件与硬件协同开发的过程。以MicroBlaze处理器为核心的系统开发可使用Xilinx公司提供的EDK(Embedded Development Kit)。该EDK提供有一个集成开发环境XPS(Xilinx Platform Studio),它同时集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试器等工具。在此环境下调用各种工具即可完成软硬件协同开发的整个流程。EDK提供有多种与MicroBlaze处理器相关的功能IP核,其中包括OPB 10/100M以太网控制器、PLB/OPB SDRAM控制器、UART中断控制器、定时器及其它外围设备接口等资源。使用EDK中的系统硬件平台设计向导(Base System Builder Wizard)可进行MicroBlaze处理器的配置,而使用添加外围设备向导(ImportPeripheral Wizard)则可调用既有IP核以生成片内设备,并与处理器总线相连。

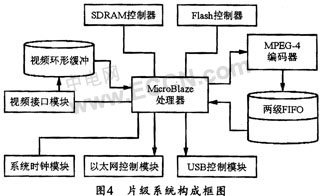

本文引用地址:http://www.eepw.com.cn/article/85844.htm本系统的片内主要功能模块包括视频接口模块、环形缓冲区、码流两级FIFO缓冲区、MPEG-4编码器、Flash控制器、SDRAM控制器、10/100M以太网控制模块、USB控制模块等。其中视频接口模块是MicroBlaze处理器与TVP5150的接口。MicroBlaze处理器对TVP5150的控制驱动程序可从TVP5150驱动程序模板移植而来,可用于实现TVP5150采集方式的配置,并将采集的视频信号以4:2:0YUV格式存储到环形缓冲区里。环形缓冲区是片内与MicroBlaze处理器总线相连的SRAM存储空间的一部分,其中数据队列的首尾指针是由MicroBlaze处理器程序维护的。采用开发工具提供的FIFO模板可对其深度、位宽、读写时钟、满标志等参数进行设定,并将两个FIFO相连以构成两级FIFO,然后将其入口与MPEG-4编码器的输出相连。FIFO的先一级与MicroBlaze处理器总线相连可支持DMA读取。MPEG-4编码器是Xilinx公司授权的MPEG-4 Simple Profile编码器IP核,它接受环形缓冲区里未压缩的4:2:0YUV格式视频信号并可将其生成MPEG-4Simple Profile格式压缩码流。MPEG-4编码器与MicroBlaze处理器总线和两级FIFO输入相连,可为EDK提供其驱动程序。Flash控制器、SDRAM控制器、10/100M以太网控制器的实现软件在EDK中已提供,其与处理器总线的连接也在向导工具中自动设定,其驱动程序就包含在其中。由于片外采用了高度集成的USB控制器,而片内的USB控制模块只是MicroBlaze处理器总线与引脚的直接相连,故其驱动程序只是参考PDIUSBD12的一般驱动程序在EDK软件平台上的移植。

本系统的片内外设与MircoBlaze处理器的连接如图4所示,其中箭头表示视频数据的流向。

3 系统软件设计

系统中的MicroBlaze处理器对TVP5150和PDIUSBD12的控制驱动程序可根据其通用驱动程序在EDK软件平台上移植生成。利用Xilinx公司提供的IP核可以搭建FPGA片内硬件平台,同时可获得底层硬件驱动程序的支持,然后在此基础上进行系统应用程序的开发。

外部模拟视频信号经TVP5150转换为数字视频信号后,即可进入FPGA并通过视频接口模块直接排列到内部环形缓冲区数据队列的队尾。

当MircoBlaze处理器接收到MPEG-4编码器可用中断时,系统将检测环形缓冲区是否为空。非空时,可将数据队列的头部数据取出送给MPEG-4编码器,同时启动编码器编码。

视频信号经过编码器编成视频原码流后,即可进入FPGA内部二级FIFO缓存。当FIFO先一级满时向MircoBlaze处理器发出数据输出中断请求。

MircoBlaze处理器响应来自FIFO的中断后,可将FIFO先一级数据取出并以USB或以太网接口输出,然后清空FIFO先一级。

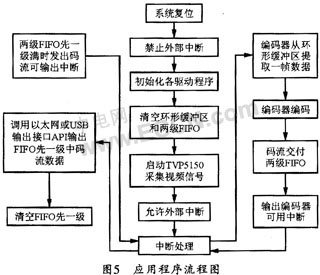

依据上面的工作过程,MircoBlaze处理器的应用程序包括以下几部分:

(1)系统复位初始化

即禁止外部中断,初始化各驱动程序,清空环形缓冲区和两级FIFO,检测USB接口、以太网接口连接以决定用何种方式输出,然后启动对TVP5150的控制并进行数据采集,最后启用外部中断。

(2)编码器可用中断服务

编码器完成一帧数据编码即可向MircoBlaze处理器发出中断,然后由MircoBlaze处理器控制编码器向环形缓冲区提取数据,并在环形缓冲区耗尽时等待一定时间;

(3)码流可输出中断服务

当两级FIFO先一级所准备输出的码流满时,可向MircoBlaze处理器发出中断,然后在MircoBlaze处理器控制下,将该码流交付给USB或以太网输出接口API并由底层驱动输出,最后再清空FIFO先一级。

图5所示是其应用程序流程图。

4 结束语

本设计介绍了基于Spartan-3 FPGA实现通用视频采集系统的实现方案。本系统的设计依赖于专用的设计软件和IP模块。由于采用了SOPC技术,该系统可裁减、可扩充、可升级,而多层次IP模块的高度复用又使得本系统具有设计周期短,风险投资小和设计成本低等优势。

评论