针对PCMCIA调制解调器设计的钽电容器解决方案

简介

本文引用地址:https://www.eepw.com.cn/article/81645.htm为适应移动计算的需求,无线网络存取技术正快速发展。全球移动通信系统(GSM)网络及通用分组无线业务(GPRS)也因此广泛应用于各行各业。为支持PDA及移动电话等基于网络技术的产品发展,2.5G基础设施的建设正在加速进行,由此产生了对笔记本电脑在网络存取技术方面所需外围设备的需求。工程师们纷纷把目光投向个人计算机存储卡国际协会(PCMCIA)定义的总线,普遍将其作为实现GSM调制解调器设计的一种解决方案。

研究表明,GSM传输由需要高强电流的相对短脉冲构成。 用于该应用程序的发送器工作电压为3.0V,其峰值电流为2A。 然而,PCMCIA总线规格使得最大可用电流仅为1.0A, 该规格显然无法满足需求。 因此,设计人员不得不考虑使用大容量电容(1000mF 至5500mF),以便在传输期间维持电压并提供所需电流。

PCMCIA调制解调器设计人员可用的电容器解决方案一直以来仅限于电化学双层电容器(EDLC)技术,该技术可保障极高电容量。 本文将指出,在时间与温度方面伴有不稳定性的高等效串联电阻(ESR)将对脉冲应用造成严重限制。 因此,EDLC并非最有效的解决方案。 要达到最佳性能,设计人员须考虑使用高电容-电压(CV)、高效容量及低ESR的钽电容器。 因其电容量仅在680mF以内(明显不足),业界一直未考虑使用此类器件。 但超高电容量钽电容器的发展为调制解调器设计人员提供了新的良机。以表面贴装封装的此类电容器电容量值高达3300mF,从而为此棘手问题提供了解决方案。

为方便说明问题,我们的讨论将主要围绕使用PCMCIA总线的GSM调制解调器而展开,然后对此类概念在脉冲功率应用(使用其他功率限制型总线结构,如USB总线等)中的应用方式进行说明。

问题总结

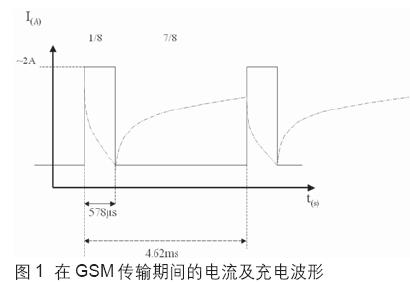

如图1所示,GSM信号以216Hz(4.62 ms PRI)的速率在载体中传输,并采用一次性划分(包括产生577ms 脉宽的1/8周期)。 这要求电容器使用剩余的7/8周期进行再充电。 以此为例,假设功率放大器要求的电流为2A。最坏的可能性是,传输期间所需功率完全由电容器提供,因此而忽略了PCMCIA总线可提供的电流。

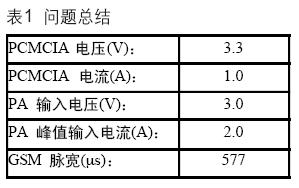

在具备由PCMCIA总线提供的3.3V工作电压及诸多功率放大器所需3V最低输入电压的情况下,允许产生0.3V的最大电压降。 表1总结了设计制约条件,而图2则对简化电路图进行了说明。

电路中的电压降包括两部分:与电容器内部阻抗(近ESR)相关联的电阻压降及脉冲结束时的电容器电压降。 因此,总电压降计算公式如下:

V = IR + I(t/C)

其中:V=电压降(V);I=电流(A);R=电容器内部阻抗—ESR(Ohm);t=脉宽(s);C=电容(F)。

备选设计方案

可用备选设计方案见表2内数据。针对该设计问题,我们应对四种潜在解决方案进行论述。其中两种用于展示钽解决方案对该设计的影响,另外两种将着重阐述利用EDLC技术的结果。解决方案1允许使用三个钽电容器,提供总量为6.6mF的电容;而解决方案2则使用两个钽电容器,组合总电容为4.4mF。除总电容量之外,这两种解决方案在ESR方面也有所差异。

同样,在探索使用EDLC技术时,我们也应考虑两种解决方案。解决方案3为EDLC,提供22mF的额定电容。解决方案4较解决方案3而言提供更大的电容及更低的ESR。

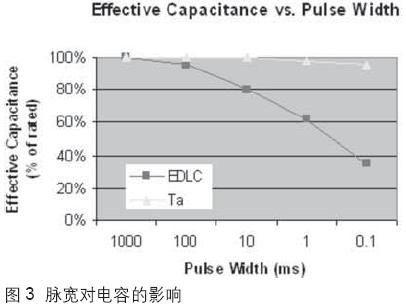

鉴于EDLC的内部组成,与使用传统电介质的电容器相比,器件以较慢速度对电场做出响应。 因此,可用(或有效)电容为图3所示脉宽的强大功能。若为GSM传输中使用的脉宽(577ms),现今市场所售EDLC的有效电容为额定电容值的3% - 48%。 以此为例,我们对EDLC技术的有效电容的发展趋势将有最乐观的预计。

方案1

设计三个并联钽电容器可提供的总电容为6.6mF。 图4就等效电路进行演示,展示了电容及器件的内部阻抗。 鉴于器件为并联方式,总电容计算公式如下:

CT=C1+C2+C3=6.6mF

有效内部ESR总值计算公式如下:

RT=1/(1/R1+1/R2+1/R3)

若R1=R2=R3,等式简化为:

RT=R/3

因此,有效ESR = 35 m?3 = 12 m?得出:

V=(2A×0.012?+(2A×[0.000557s/0.0066F])

V=0.02V+0.17V

V=0.20V

从上述计算公式可以看出,钽电容器的低内部阻抗导致最小内部IR损耗。 得出的0.2V总电压降在设计制约因素以内(允许最大值为0.3V)。

方案2

如解决方案1所示,解决方案2的有效ESR计算公式如下:

ESR=35m?2=18m?得出:

V=0.04V+0.26V

V=0.30V

虽然在设计制约条件以内,但0.3V的电压降不会在设计中保留余地。

方案3

检查EDLC后可以发现:

V=0.40V+0.10V

V=0.50V

高ESR成为造成总电压降的主要因素,得出的0.50V总电压降超出电路设计允许范围。

方案4

最后,检查高电容/低ESR EDLC解决方案:

V=0.30V+0.07V

V=0.37V

低ESR可能会对计算的电压降产生有利影响。 不过,电容的增加对整体性能几乎没有影响。 虽然低于解决方案3所示值,本方案中的总电压降仍然超出设计制约条件。该解决方案的另一弊端在于设备的尺寸。4.8mm的高度对于PCMCIA卡标准之形状因数以内的使用并不十分理想。

为克服与ESR相关联的过剩电压降,采用EDLC技术的设计人员须考虑使用其他电路(如DC-DC引导转换器)。该设计方案在耗尽宝贵插板空间的同时,还将产生额外电路成本。

如前所述,电路对ESR的依赖是设计中需要考虑的重要因素之一。 各解决方案中所述计算方式基于指定为25 ℃的初始ESR。 必须考虑对ESR对电路的造成的影响进行更为深入彻底的分析:

·ESR在温度方面的稳定性,及最终产品寿命老化引起的ESR可变性。

通过对现有技术的调查发现,EDLC中的ESR在其指定工作温度下与钽(其ESR在相同温度范围内保持在指定水平)相比差异可达400%。设计人员还须考虑到如下事实:在部件使用寿命内,EDLC ESR将随着老化情况而增加。

表3就钽ESR性能与EDLC技术进行了对比。就钽而言,ESR在温度及时间方面均比较稳定,在全工作温度或寿命试验中不发生规格变化。对于笔记本电脑内即定的PCMCIA卡工作环境而言,ESR保持85 ℃的稳定性是非常理想的情况。

对比而言,EDLC技术中的ESR差异在脉冲应用中则较为麻烦。 如上述电路分析所示,与EDLC中的ESR相关联的电阻降压已是总体电压降的主导因素。鉴于 ESR 的高可变性,难以在各种条件下以足够的裕度设计电路。

结语

对脉冲功率应用中大容量电容的需要而言,设计人员须意识到:ESR是关键因素。 超高电容(甚至过剩电容)无法克服与高ESR解决方案相关联的效率损耗。用额外电路克服此类损耗(如引入转换器的使用)不仅成本高,也占用宝贵的插板空间,从而加大设计的工作量。另外,选择充足电容量的解决方案(配合低ESR)将会创造更高效率及成本有效性。

评论