IIC总线在LonWorks神经元芯片FT3150中的应用

目前比较常用的串行总线有:IIC(Inter Integrated Circuit)总线、SPI(Serial Periphcral Interface)总线和Micro-wire总线等。其中,IIC总线是Philips公司于80年代推出的一种二线制总线,它通过一根串行数据线(SDA))和一根时钟线(SCL)在互连的器件间传输信息。这对具有有限个I/O引脚的神经元芯片来说,节约了I/O引脚开销,方便了系统进一步扩展。

LonWorks总线为用户提供了一个针对实际工程应用的神经元芯片--Neuron芯片。Neuron芯片高度集成,所需外部器件较少。它包含3个处理七层LonTalk协议的8位处理器,即媒体访问控制处理器、网络处理器和应用处理器。芯片内部有11个通用I/O引脚,根据实际需要对11个引脚进行编程,形成多达34种不同类型的I/O功能,包括并行I/O、串行I/O、定时/计数器等等。一个Neuron芯片可连接一个或多个物理I/O设备,如温度和位置传感器、阀门、开关以及LED。神经元芯片同件通过执行特定的I/O对象来管理这些设备的接口。Neuron芯片分为3150和3120两类,Neuron3150支持外部存储器,适合更复杂的应用,而Neuron3120本身带有ROM,不支持外部存储器。

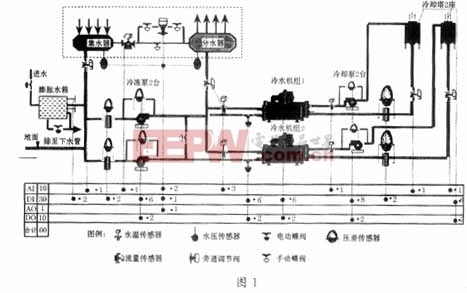

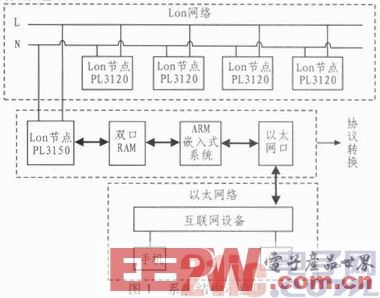

美国Echelon公司新推出了新的神经元芯片--自由拓扑智能收发器FT3150如图1所示。FT3150是在Neuron 3150处理器的基础上集成了一个自由拓扑双绞线收发器,既降低了成本,又减小了接口电路功耗。FT3150芯片内部有2kBRAM和0.5kB EEPROM存储器,通过对外引出地址及数据总线用户可方便地扩展RAM数据存储器和flash固件、程序存储器,总扩展存储器空间最多为64k。FT3150 芯片服务引脚主要用于节点配置、安装与维护。与FT3150配合使用的是Echelon公司的FT-X1(穿孔)或者FT-X2(表面贴)通信变压器,对电磁干扰和高频共膜噪声有较强的抗干扰能力。这使得LonWorks神经元芯片FT3150达到一个更高性能、更稳定、更经济的新层次。

IIC总线技术

IIC总线是微电子通信控制领域中被广泛采用的一种总线标准,具有接口线少,控制方式简单、器件封装外形小、通信速率高等特点。它仅通过两根线SDA和SCL即可实现完善的全双工同步数据传送,能够十分方便地构成多主机系统和外同器件扩展系统。

IIC总线数据传输只有任总线处于空闲状态时(SCL和SDA必须保证为高电平)才启动。IIC总线协议定义数据传输时序如图2所示,起始条件为当SCL为高电平时,SDA由高电平向低电平跳变,数据开始传输;结束条件为当SCL为低电平时,SDA由低电平向高电平跳变,数据传输结束。传输过程中,当SCL高时,SDA必须始终保持稳定状态,此时出现任何跳变都被认为是起始或停止条件,只有当SCL为低电平的时候才允许SDA上的数据改变。

IIC总线上的数据格式如图3所示,由起始位(S)、从机地址码、读写控制位(R/W)、应答位(A)、数据和停止位(P)等组成。通信启动时,主器件先发送启动信号和从机地址,总线上每个器件都有自己的唯一地址,与地址与某一从器件相匹配时,该从器件发一应答位,主器件则认为寻址成功,然后根据R/W位确定的数据传送方向进行数据传输。若主器件长时间收不到应答位,则认为超时,放弃本次数据传输。通信停止时,主机发送一个停止信号。

FT3150的IIC总线技术应用

神经元芯片FT3150所支持的串行I/O功能包括:Bitshift、IIC和Neuronwire(SPI)等。IIC I/O用于实现FT3150芯片与遵循IIC串行总线规约的器件相连。由于IIC总线是各种总线通信中使用信号线最少,并具有自动寻址,多主机时钟同步和仲裁等强大的功能,因此,使用IIC设计计算机系统十分方便、灵活,体积也小,各类实际应用比较广泛。

数据通信的硬件连接

FT3150一般总是主控器,它定义108(14脚)管脚为时钟线(SCL),109(15脚)管脚为串行数据线(SDA),或者100(2脚)管脚为时钟线(SCL),IO1(3脚)管脚为串行数据线(SDA)。这些IO线的漏极开路以满足IIC规约的特殊需要。实际Neuron芯片与IIC器件的连接,只需存引脚上增加两个上拉电阻,而不再需要其他外部元件。

我们在开发LonWorks智能电动阀门时,采用EEPROM24WC16作为FT3150芯片读写数据的存储器,用来记录历史数据,防止掉电丢失。24WC16是采用CMOS工艺制成的2K*8位的电可擦除存储器,内部存储空间共分8页,具体读写页数由其串行总线地址的最低三位A0、A1和A2决定,每页最多可存储256字节数据。为了实现FT3150芯片与24WC16的通信,将神经元芯片上IIC总线引脚IO9与24WC16的SDA相接,IO8与24WC16的SCL相接,通过编程产生操作时序从而实现FT3150芯片对24WC16有关寄仔器的写入和读出。值得注意的是:由于IO8和IO9都是硬件开漏状态,为了避免端口吸收太大的电流,数据总线SDA和时钟总线SCL一定要接足够大的上拉电阻。24WC16与FT3150芯片硬件连接如图4所示。

数据通信的软件编程

FT3150与24WC16通信的软件编程采用专门为LonWorks神经元芯片没计的的Neuron C。Neuron C是从ANSI C中派生出来的并进行了增删,它的扩展直接支持神经元芯片的固件。Neuron C的编程主要是神经元芯片的事件凋度、I/O事件、网络变量和显式消息等。

IIC数据传输中的控制字R/W位由io_in()/io_out()函数隐式给出。同时,数据传输时需要一个计数参数对读/写的数据字节数进行控制,但一次最多读/写255个字节。IIC总线寻址采用右对齐的7位设备地址,对24WC16器件的8位地址:1010000R/W,则寻址的IIC器件地址为:01010000,即0x50。对于IIC输入/输出,io_in()和io_out()函数返回值0和1,分别反映传输的失败(0)和成功(1)状态。

FT3150与24WC16进行数据读写过程如下:首先把采集到的一个8个字节数据写入24WC16中指定的寄存器,然后再读回已保存的数据。源程序如下:

评论