基于Flash的FPGA实现高度安全设计

保密的重要性

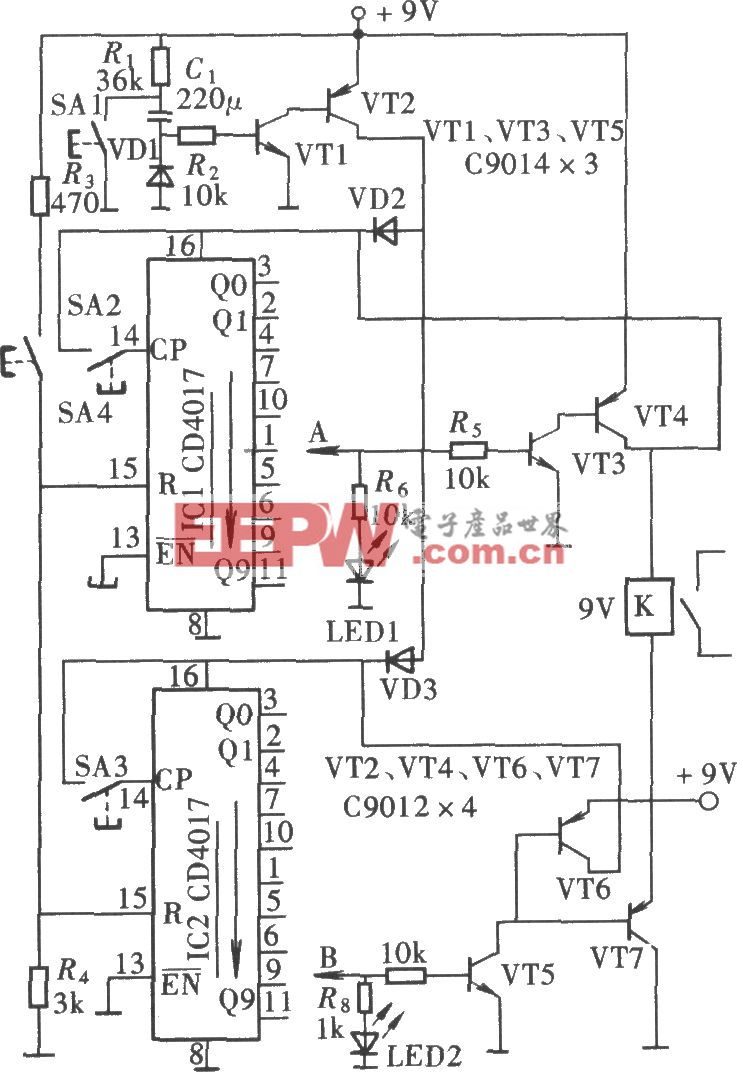

对电子系统而言,FPGA的保密性极其重要。图1列出了两个系统设计的示意图,左边为1995年所作的系统设计,在该设计中,以ASIC芯片为核心,FPGA仅起到胶合逻辑的作用;在右边2005年进行的同类型系统设计中,不难发现FPGA已经成为系统设计的核心,它整合了原有ASIC及部分ASSP芯片的功能,因此FPGA作为系统芯片直接取代了ASIC的功能。随着FPGA性能、容量与功能的不断提升,今天的FPGA 已成为系统的心脏、知识产权的集合,所以如果FPGA存在安全性问题的话,与其相关的产品将遭受严重打击。

|

保密性定义——四个对FPGA最大的安全威胁

a.克隆

克隆是指竞争对手拷贝启动 PROM 或从板上拦截处理器码流并进行复制。如果设计中包含外部码流时,则该设计的IP 对克隆非常脆弱。

b.反向工程

反向工程即竞争对手由重建您的设计原理图或网表复制您的设计。在这个过程中,竞争对手将了解设计的运作从而进行改进。

c.过建

过建在把您的产品交给无道德的合同制造商生产时出现,这些制造商能在开放市场上购买额外的FPGA元器件,然后在厂家没有允许的情况下,生产额外的产品,在没有开发成本和不需要提供技术支持的条件下,以更低的价格在市场上售卖,从而牟取利润。 d.拒绝服务

拒绝服务属于恶意破坏的行为,您的竞争对手或者黑客能够通过重新编程您系统上的 SRAM FPGA而使您的系统不能运行。拒绝服务使厂家的声誉、产品的质量等形象将遭到破坏。

Actel 第三代 Flash FPGA

在了解了保密性的定义及FPGA保密重要性的基础上,Actel推出了第三代Flash FPGA,具有众多优点与特性。

Actel第三代Flash FPGA,包括两个产品系列:ProASIC3与ProASIC3E。ProASIC3能实现30k到1M的门密度,它的容量高达144kb SRAM,具有288个 I/O ;ProASIC3E能实现600k到 3M的门密度,它的容量高达504kb SRAM,具有604个I/O。

这两个系列均具备增强的高性能结构,其时钟频率最高可达350MHz,相对于第二代产品来说,其封装密度提高了20%,而逻辑利用率超过95%。SRAM的工作频率也可达到350MHz,而且每个模块中均带有硬连线的FIFO控制功能。三个锁相环(PLL)的输出频率也可达到350MHz,并且具有灵活的相位输出、延迟、分频和倍频功能。这两个系列同样支持64 位、66 MHz的PCI总线。

作为以价值为基础的FPGA,第三代产品提供了全新的功能,包括:所有器件都带有1kb片上可配置的Flash ROM及带硬连线 的AES 解密安全 ISP。上一代产品中的FPGA的保密措施在这一系列内继续保持,如片上 FlashLockTM 安全措施及针对单电压工作而在片上集成的电荷泵。最后,需要提及的是产品支持19种不同的I/O标准,包括 LVDS等。

Actel第三代Flash FPGA具有竞争性的成本优势,因为Flash 技术可省去SRAM FPGA额外的成本负担。此外,Flash 技术还可以提供以下独特的性能:

评论