Qsys与uC/OS学习笔记2:系统仿真

仿真在FPGA设计过程中举足轻重,在板级调试前若不好好花功夫做一些前期的验证和测试工作,后期肯定要不断的返工甚至推倒重来,这是FPGA设计的迭代特性所决定的。因此,在设计的前期做足了仿真测试工作,虽然不能完全避免后期问题和错误的发生,却能够大大减少后期调试和排错的工作量。

本文引用地址:http://www.eepw.com.cn/article/275553.htm逻辑设计中需要做仿真,是因为逻辑设计大都是设计者原型开发的,不做仿真的话设计者肯定心里也没底。而用Qsys搭建的系统多是由已经成熟验证过的IP核组成的,还需要仿真否?这是个仁者见仁智者见智的问题,特权同学也无意深入其中不能自拔。过去用SOPC Builder时还确实想动手做做这类带CPU的系统级仿真,只可惜倒腾半天不是缺这个就是少那个,大都无功而返。这回上了Qsys,而且ModelSim-Altera对于Quatus II的支持也是做得越来越“体贴”了,所以今个再做了一些尝试,果然成功了,原厂把工具的使用做得越来越傻瓜便利的同时,工程师们从中大大获益。

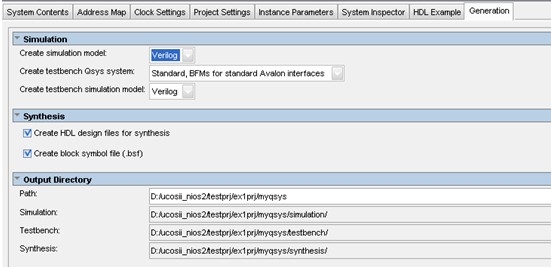

如图1所示,首先在Generations的Simulation选项中做好设置。

图1

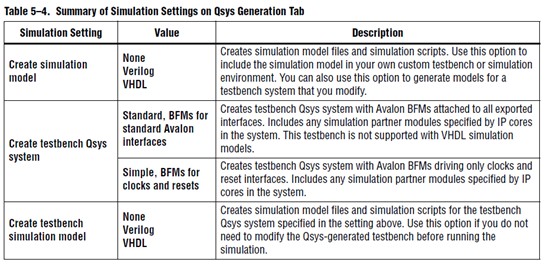

Simulation设置选项的具体含义如图2所示。

图2

因为都是用Verilog,所以simulation model和testbench simulation model我们都选择Verilog,话说Altera其实主打的是Verilog语言,所以各种功能对Verilog的支持都是非常到位的,VHDL就不一定了。也用过Xilinx的东西,则正好相反。也不能谈论孰优孰劣,也是习惯使然。

Standard和Simple的模型主要差别在于后者只是简单的在testbench里产生clock和reset信号,而前者则会对所有export信号产生激励或引出便于监视观察。

确定完成Simulation的设置后就可以点击左下角的Generate重新生成系统。

系统生成完毕,到“工程目录myqsystestbenchmyqsys_tbsimulation”这个路径下有测试脚本的顶层文件myqsys_tb.v,打开后代码如下:

`timescale 1 ps / 1 ps

module myqsys_tb (

);

wire myqsys_inst_clk_bfm_clk_clk; // myqsys_inst_clk_bfm:clk -> [myqsys_inst:clk_clk, myqsys_inst_reset_bfm:clk]

wire myqsys_inst_reset_bfm_reset_reset; // myqsys_inst_reset_bfm:reset -> myqsys_inst:reset_reset_n

wire [7:0] myqsys_inst_led_pio_external_connection_export; // myqsys_inst:led_pio_external_connection_export -> myqsys_inst_led_pio_external_connection_bfm:sig_export

myqsys myqsys_inst (

.clk_clk (myqsys_inst_clk_bfm_clk_clk), // clk.clk

.reset_reset_n (myqsys_inst_reset_bfm_reset_reset), // reset.reset_n

.led_pio_external_connection_export (myqsys_inst_led_pio_external_connection_export) // led_pio_external_connection.export

);

altera_avalon_clock_source #(

.CLOCK_RATE (50)

) myqsys_inst_clk_bfm (

.clk (myqsys_inst_clk_bfm_clk_clk) // clk.clk

);

altera_avalon_reset_source #(

.ASSERT_HIGH_RESET (0),

.INITIAL_RESET_CYCLES (50)

) myqsys_inst_reset_bfm (

.reset (myqsys_inst_reset_bfm_reset_reset), // reset.reset_n

.clk (myqsys_inst_clk_bfm_clk_clk) // clk.clk

);

altera_conduit_bfm myqsys_inst_led_pio_external_connection_bfm (

.sig_export (myqsys_inst_led_pio_external_connection_export) // conduit.export

);

endmodule

该代码中首先例化了被测试系统myqsys,将其3个export信号引出。然后分别针对这3个export信号产生相应的激励和响应,即altera_avalon_clock_source用于产生clock,altera_avalon_reset_source用于产生reset信号,altera_conduit_bfm则用于观察led_pio输出。这三个模块的详细代码都可以在同目录的submodules子文件夹下找到。

接下来,我们需要打开EDS中的软件工程并对其进行仿真。我们接着使用上一个笔记中创建的countbinary_prj工程进行仿真,首先我们需要到BSP Editor里面去重新generate,因为Qsys有改动并重新生成了。接着修改其main函数如下:

int main(void)

{

alt_u16 cnt;

for(cnt=0;cnt<256;cnt++)

{

IOWR_ALTERA_AVALON_PIO_DATA(LED_PIO_BASE,cnt);

}

while(1);

}

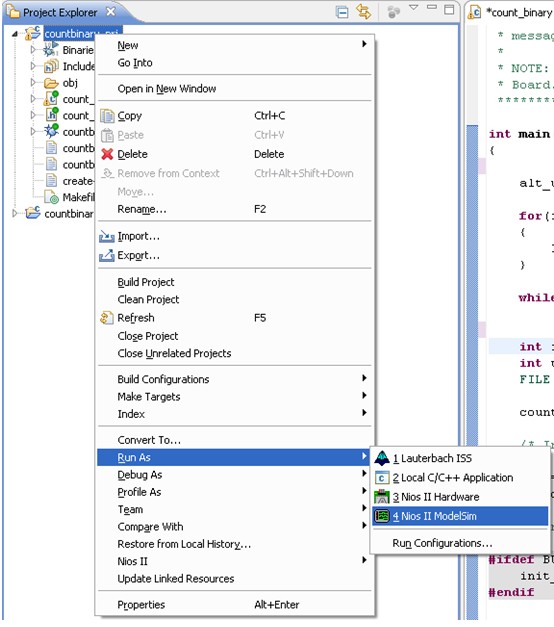

目前工程代码执行的意图是:在上电初始化完成后,led_pio会从0连续的递增一直到255,然后停止。保存修改的软件代码并重新编译工程,然后在应用工程上点击右键值并选择Rus asàNiso II ModelSim,如图3所示。

图3

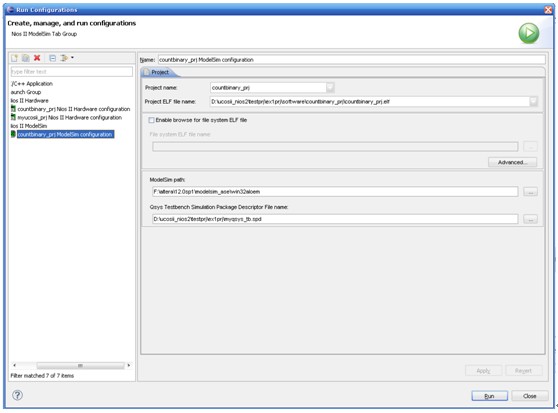

第一次运行通常会弹出如图4所示的窗口,需要对仿真选项做一些配置。选择选择仿真的工程名(Project name)、仿真的elf可执行文件(Project ELF file name)、ModelSim软件的安装路径(ModelSim path)和Qsys测试脚本封装描述文件(Qsys Testbench Simulation Package Descriptor File name)存储位置。设计好后点击Run即启动ModelSim进行仿真。

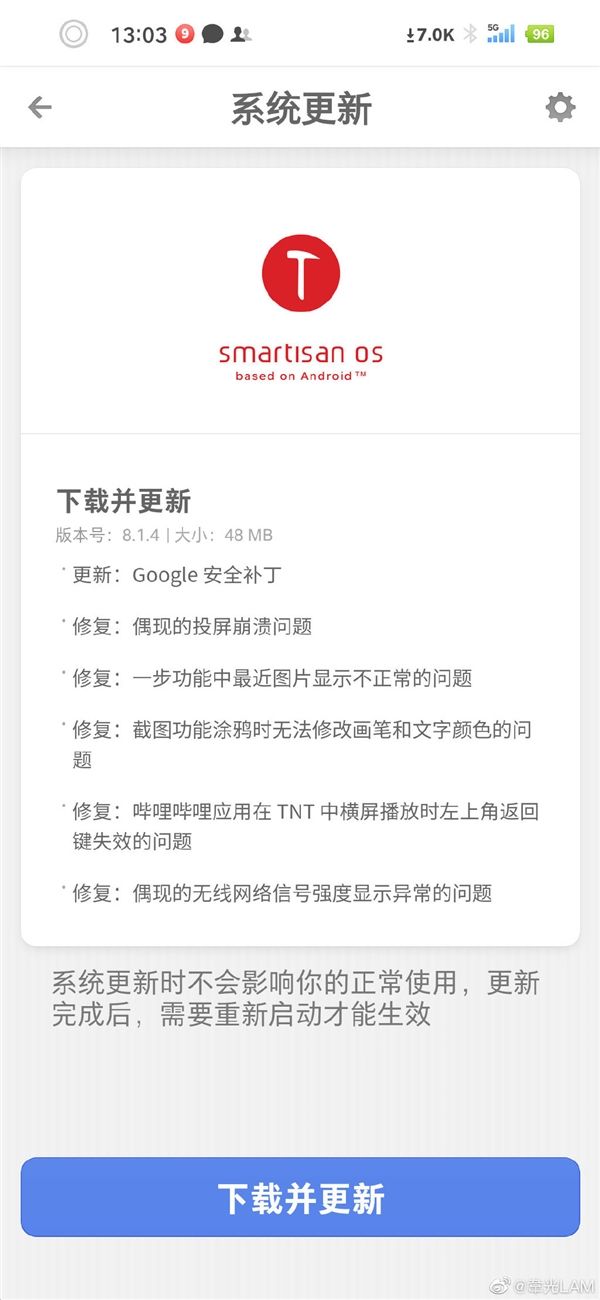

图4

弹出ModelSim-Altera后,我们可以讲顶层文件的3个export信号添加的Wave窗口中,然后Run起来,看看仿真时间有2-3秒后我们可以回放仿真波形(具体的时间需要看PC的状况,特权同学的Pentium E5800跑了应该有半分多钟),如图5、图6和图7所示。

如图5,刚上电0ns开始,reset信号有一段时间的低脉冲,大约50个clk周期,正如我们的testbench中所设计的。

图5

如图6所示,在仿真进行到大约1.3s时刻,led_pio信号有一段变化的波形,初始0值在经过这段变化波形后最终变为255,这也是我们软件代码里面所设置的最终值。

图6

再来看图7,我们将led_pio的变化段波形放大,果然是我们软件编程的递增的值,一直从0递增到255为止。

图7

仿真的流程基本就是这样,很easy,我们只要动动指尖就可以完成,当然了,如果要做很多个性化的细致的仿真验证,那么在testbench里面我们倒是可以动些手脚,输出结果也不光只是看看波形而已。

评论