超宽带(UWB)定位系统发射机基带的系统设计,功能模块分解、硬件实现

4.1.2主控单元mcu

主控单元MCU的工作任务在上一章节中已经做了详细的描述,它控制这整个发射机基带处理系统的正确运作,通过与MAC层进行交互动作,接收MAC层发送的数据信息,并且生成个模块所需要的控制信息。

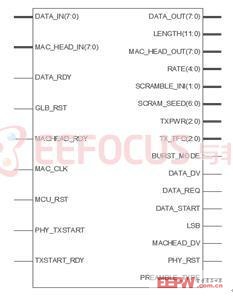

图4.5 MCU模块框图

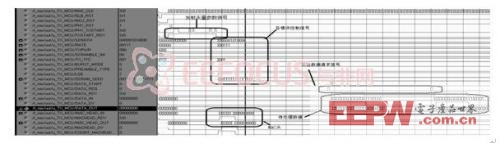

对工程文件进行综合、布局布线后仿真,得到如图4.6所示结果,可以看到MCU正确的输出了各级控制信号,并且按照正确的时序输出MAC头和待处理数据。

图4.6 MCU 仿真结果

使用Chipscope添加观察信号采样时钟、触发信号和待观察信号,重新综合、布局布线生成bit文件,下载到目标板后用ChipScope进行在线测试,得到观测结果如图4.7所示。通过仿真结果和在线测试结果的对比,可以验证设计的正确性。

图4.7 MCU在线测试结果

4.1.3扰码模块

扰码器的硬件实现框图如下图所示。

图4.8 扰码模块硬件实现图

因为MCU传输过来的数据帧是以字节为单位并行传输的,因此在加扰前,需要将并行的数据转换为串行数据,具体实现时,加入一个串并转换模块来进行并串转换。

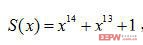

本文扰码器模块的伪随机序列生成多项式为: ,扰码种子编号为00,初始状态设为15’b0011_1111_1111_111,这样通过一个15位的移位寄存器进行循环移位,产生所需的伪随机序列,然后将输入值与伪随机序列进行异或(模2加法),从而实现扰码。主要实现代码如下:

,扰码种子编号为00,初始状态设为15’b0011_1111_1111_111,这样通过一个15位的移位寄存器进行循环移位,产生所需的伪随机序列,然后将输入值与伪随机序列进行异或(模2加法),从而实现扰码。主要实现代码如下:

|

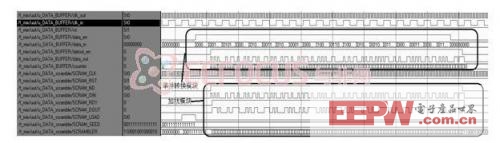

对工程文件进行综合,布局布线仿真,得到如图4.9结果。

图4.9 扰码模块仿真结果

在图4.9中 data_in为MAC层发送的8位并行数据,SCRAM_DIN为经过并串转换之后的串行输出的数据,SCRAM_DOUT为经过扰码处理后的输出,当SCRAM_LOAD为高时,对扰码器内部反馈移位寄存器SCRAMBLER进行初始化,并且在数据输入有效期间,线性反馈移位寄存器SCRAMBLER进行移位操作。

将仿真通过的工程文件使用ChipScope 添加观察信号采样时钟、触发信号和待观察信号后重新综合、布局布线生成bit文件,下载到目标板后用ChipScope 进行在线测试,设定DIN_CLK为ChipScope采样观测信号所用的时钟,得到如图4.10所示观测结果,图4.10的在线测试结果与图4.9的后仿真结果吻合,验证了设计的正确性。

图4.10 扰码模块在线测试结果

pa相关文章:pa是什么

评论