超宽带(UWB)定位系统发射机基带的系统设计,功能模块分解、硬件实现

第4章基带系统各模块的实现及测试

4.1各个模块的实现

4.1.1时钟产生单元

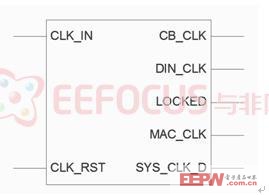

整个发射机基带数字处理系统工作时一共需要四个不同频率的时钟,时钟生成单元通过一个DCM和一个8分频的计数器使用外部输入时钟生成需要的所有时钟。时钟生成模块的端口定义如表4. 1所示,模块框图如图4.2所示。

表4.1 时钟生成模块的端口定义

端口名 | 位宽 | 输入/输出 | 说明 |

CLK_IN | 1 | 输入 | 外部输入时钟 |

CLK_RST | 1 | 输入 | 复位接口,接全局复位信号 |

MAC_CLK | 1 | 输出 | MAC层时钟 |

DIN_CLK | 1 | 输出 | 物理层时钟 |

CB_CLK | 1 | 输出 | 信道编码后输出数据时钟,根据编码方式不同而不同 |

SYS_CLK_D | 1 | 输出 | QPSK调制后输出数据时钟,1/2倍的CB_CLK |

LOCKED | 1 | 输出 | 时钟输出有效信号 |

图4.2 时钟产生模块框图

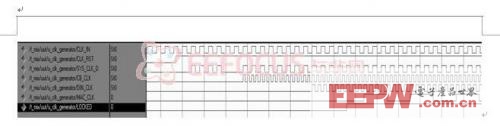

由于本论文采用的是3/4编码速率,因此,CB_CLK时钟频率为DIN_CLK的4/3倍。对整个模块进行布局布线后仿真,仿真结果如图4.3所示

图4.3时钟产生模块仿真结果

将时钟生成模块下载到目标器件后,使用在线片内信号分析仪ChipScope 观察得到的波形如图4.4所示,由于ChipScope采样观测信号所用的时钟设定为时钟模块频率最高的CB_CLK,对于频率为CB_CLK3/4倍的DIN_CLK采样结果有较大的偏差,而对于MAC_CLK与CB_CLK也不是整数倍关系,因此也达不到占空比相等的脉冲显示。

图4.4 时钟产生模块在线测试结果

pa相关文章:pa是什么

评论