Rapid IO---成就高速互连之美

在过去的30多年时间内,处理器的主频和性能呈现指数上升的趋势,而与之相对应的处理器总线传送能力的增长却相对缓慢的多,这就导致了由时钟频率表征的CPU的性能和由总线频率表征的CPU可用的总线带宽之间的差距不断在变大,互连总线成为高速运算和处理系统的瓶颈。现代的高性能计算系统和网络存储系统需要更高速率的数据传送。高带宽、低延迟,高可靠性成为衡量一个总线技术的基本要求。

本文引用地址:https://www.eepw.com.cn/article/258683.htm

一、 传统总线的问题:

传统总线多采用并线总线的工作方式,这类总线一般分为三组:数据线,地址线和控制线。实现此类总线互连的器件所需引脚数较多,例如对于64位数据宽的总线,一般由64根数据线,32-40根地址线以及30根左右的控制线,另外由于半导体制造工艺的限制还要加上一定数量的电源引线和地线,总共会有约200根左右的引线,这给器件封装、测试、焊接都带来了一些问题,如果要将这种总线用于系统之间的通过背板的互连,由此带来的困难就可想而知。

为了提高总线的传输能力,传统总线多采用增加数据总线的宽度或是增加总线的频率的方式来实现。如PCI总线支持25M、33M、50M、66M的工作频率,PCI-X总线是在PCI总线结构的基础上进得到的一种总线结构,在硬件和软件上兼容PCI总线,PCI-X总线可以支持32bit、64bit的总线,其工作频率为66M、133M,对于64bit的PCI-X,如果其总线工作频率为133MHz,其峰值传送带宽可达到133×64bit=8.512Gbps。目前PCI-X也有一些版本定义了总线频率为266MHz或者533MHz的总线,另外也有一些总线定义了数据宽度为128bit 或是256bit的总线,但很少有人会选用这样的总线,因为增加总线频率和数据带宽虽然一定程度上满足了人们对高速数据传送的需求,但同时也带来了一些新的问题。更宽的总线导致器件引脚数的增加,从而增加封装尺寸,当然带来成本上的增加。

另一个问题是当总线的工作频率超过133MHz时,很难在一条总线上支持超过两个外部设备,在总线上增加器件相当于增加容性负载,而容性负载的增加意味着装载或排空电荷使总线达到所需的额定电平的时间增长,信号的上升和下降时间的增长会限制总线的工作频率。对于并线总线的另一个问题是时钟与信号的偏移容限的问题,对于这样一组并行信号线的集合,信号的采样是取决于时钟信号的上升沿或是下降沿,这样对于信号的跳变和时钟的跳变时刻的时间差就有一个上限值,随着速率的升高,布线长度、器件门电路自身的翻转时间都会影响总线的速率。

用于处理器之间互连以及背板互连的另一个主要技术是以太网,近些年来,以太网在存储、电信、通讯、无线、工业应用以及嵌入式应用中得到大量的应用,现有的成熟的硬件和协议栈降低了开发的复杂性和产品的开发成本。但是在局域网和广域网中得到很好应用的以太网用于这种芯片级或是板极的系统互连显示出了低效率、高延时的特性,QOS需要高层软件的参与,造成软件模块化结构不清晰。尤其是当背板的传输速率从1Gbps增加到10Gbps时,增加的处理要求已经超出了以太网的能力。

二、什么是Rapid IO?

Rapid IO技术最初是由Freescale 和Mercury 共同研发的一项互连技术,其研发初衷是作为处理器的前端总线,用于处理器之间的互连,但在标准制定之初,其创建者就意识到了RapidIO还可以做为系统级互连的高效前端总线而使用。1999年完成第一个标准的制定,2003 年5月,Mercury Computer Systems公司首次推出使用Rapid IO技术的多处理器系统ImpactRT 3100, 表明Rapid IO已由一个标准制定阶段进展到产品阶段,到目前为止,Rapid IO已经成为电信,通迅以及嵌入式系统内的芯片与芯片之间,板与板之间的背板互连技术的生力军。

Rapid IO 是针对嵌入式系统的独特互连需求而提出的,那么我们首先来说明嵌入式系统互连的一些基本需求:嵌入式系统需要的是一种标准化的互连设计,要满足以下几个基本的特点:高效率、低系统成本,点对点或是点对多点的通信,支持DMA操作,支持消息传递模式交换数据,支持分散处理和多主控系统,支持多种拓朴结构;另外,高稳定性和QOS也是选择嵌入式系统总线的基本原则。而这些恰是Rapid IO期望满足的方向。所以Rapid IO在制定之初即确定了以下几个基本原则:一是轻量型的传输协议,使协议尽量简单;二是对软件的制约要少,层次结构清晰;三是专注于机箱内部芯片与芯片之间,板与板之间的互连。

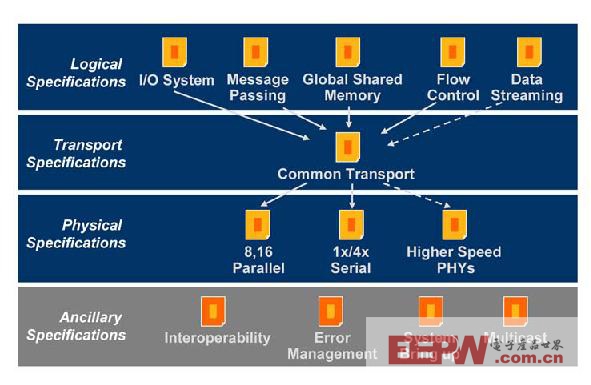

Rapid IO采用三层分级的体系结构,分级结构图如下图所示:

由此图可见,Rapid IO协议由逻辑层、传输层和物理层构成。最明显的一个特点就是Rapid IO采用了单一的公用传输层规范来相容、会聚不同的逻辑层和物理层,单一的逻辑层实体增强了Rapid IO的适应性。

物理层定义了串行和并行两个实体,得到广泛应用的只有串行方式,尤其是用在背板互连的场合,串行方式可以在两个连接器之间允许80-100cm的连线,单链路传输带宽可达10Gbps。目前Rapid IO的标准是Version1.3,在未来的Version2.0规范中定义了更高的传输速率,可以得到更高的传输带宽。

物理层:

Rapid IO规范中定义的最低层是物理层,最初定义的是并行总线,之后定义了串行总线,并线总线可以选择8位或16位的宽度,传输电平采用LVDS方式,时钟信息在一对单独的差分线上传送,不在数据流中编码,频率在250M-1.0G之间。相比串行总线而言,无多少优点可言,所以只是在最初有支持这种总线的芯片出现,目前几乎所有的物理层均采用了串行方式。

串行物理层定义了器件间的全双工串行链路,在每个方向上支持1个串行差分对称为1个通道(1x),或同时支持4个并行的串行差分对称为4通道(4x),接口的电气特性采用成熟的XAUI(10GbE Attachment Unit Interface)接口,编码方式采用的是8B/10B编码,对链路的管理,包括流量控制,包定界和错误报告等使用专用的8B/10B码(即K码),接收端从链路上提取时钟信息,无需独立的时钟线。每一个通道支持三种不同的传送波特率1.25G,2.5G,3.125G(与之相对应的数据速率分别是1.0G,2.0G,2.5Gbps)。

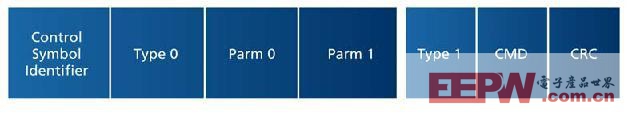

图:Control symbol 包的结构

Rapid IO是一种基于可靠传送的协议,每一个数据据包的传送均要求对端在物理层上响应一个控制符号包,此包是一个4个字节的数据包,表明了数据包的传送状态,数据包是否被对方接方,还是要求重新发送或是包未被接收。发送方和接收方均可以使用控制符号包来获得对方的状态。

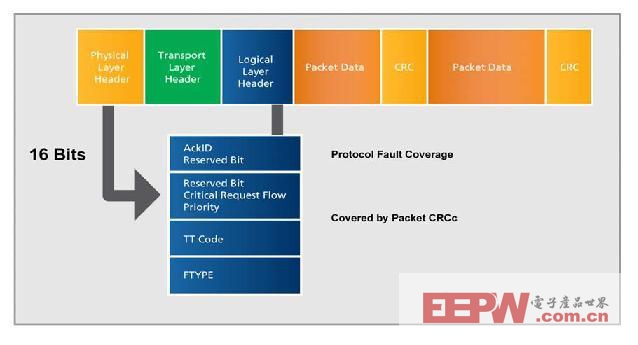

图:Rapid IO包结构及物理层组成

评论