全新6核DSP:低功耗高性能一个都不能少

当前,多核DSP已成为DSP发展的主旋律,多核对于性能的提升毋庸置疑,但它带来的功耗与板级空间问题同样不容忽视。对于DSP厂商而言,提供具有高性能且极佳电源效率的芯片已成为赢得市场的必要条件。

本文引用地址:https://www.eepw.com.cn/article/257537.htm日前,TI即推出其全新的6核DSP处理器,在实现高达4.2GHz的处理能力的同时,仅有0.15mW/MIPS的低功耗,完美契合了高性能、严格功率预算的应用所需。

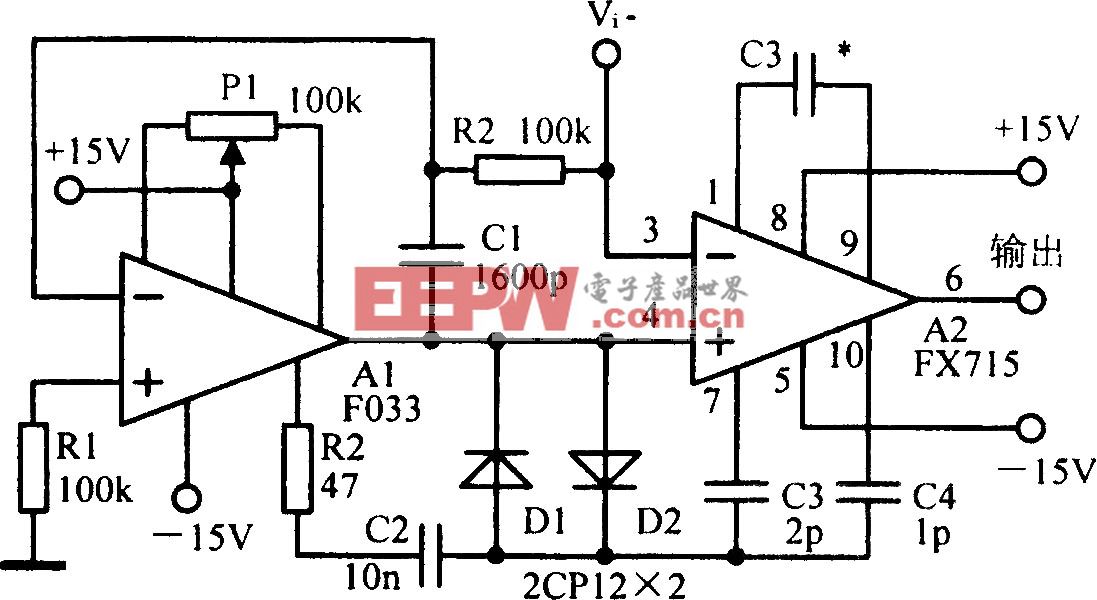

TMS320C6472内部集成6 颗高速 C64X+ DSP 内核,运行频率为 500MHz、625MHz、700MHz。相对于TI C64+系列,其内核的数目翻了一倍,但功耗却不升反降。在功耗上,TI设立了一个新的标准,即新的极限——在实现3GHz性能的基础上,其每MIPS的功耗仅为0.15mW。

TMS320C6472可实现4.2GHz/33600 MMAC,具有4.8MB 片上 L1/L2 RAM。其两级的缓存设计,令每个DSP核既有单独的也有共享的Cache,从而提高了存储与运算的性能。

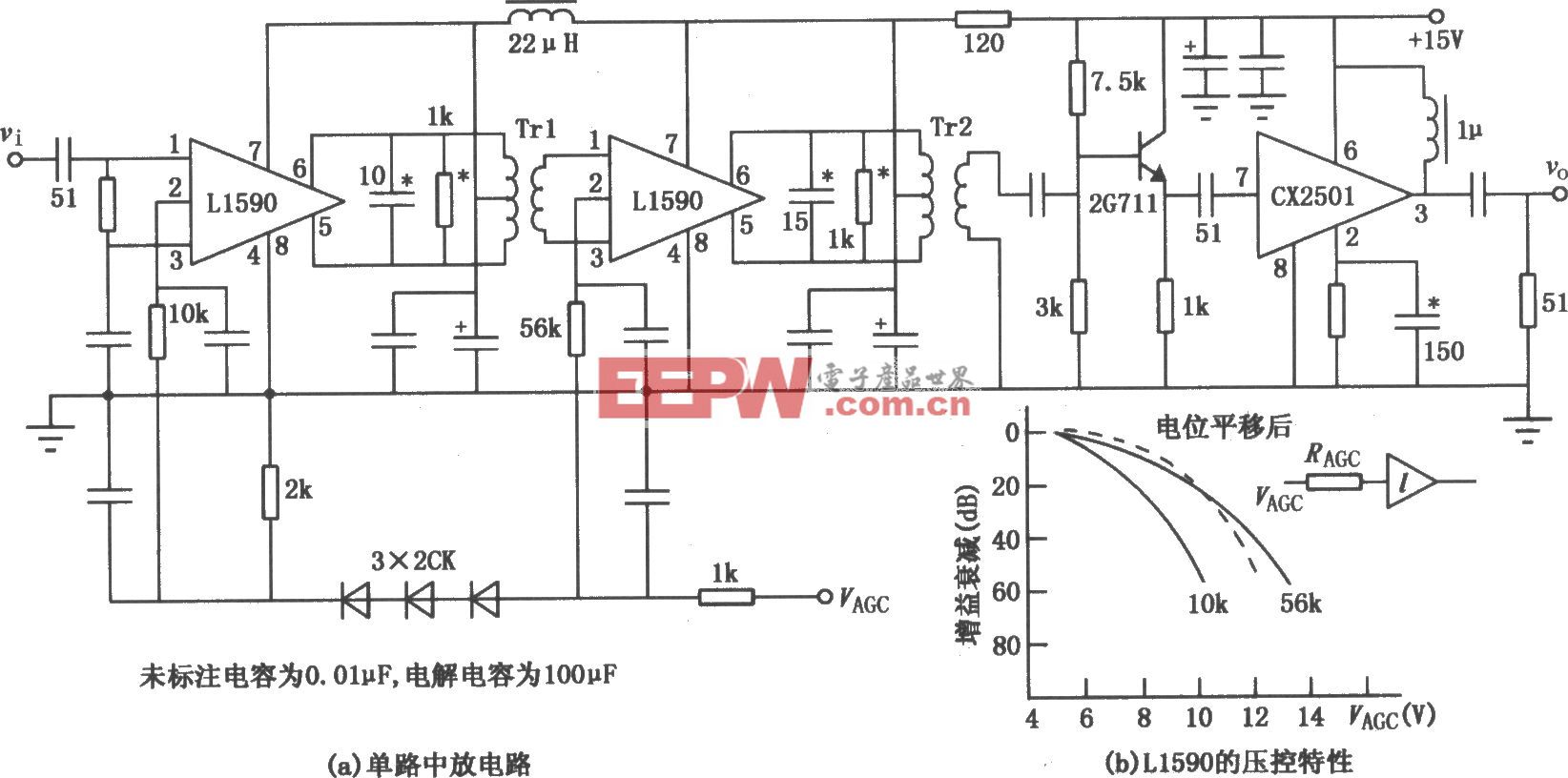

TI通用DSP业务发展经理郑小龙先生介绍了TMS320C6472所采用的优化的DSP架构。

为了使6核间很好地协调工作,TI设计了良好的管理和协调机制,体现在:一方面,TMS320C6472具有两级缓存设计,即除了每个内核都具备专用的 L1 和 L2 存储器外,还具备每个数据存储器 768KB 的共享 L2 程序以及共享存储控制器。另一方面,为了便捷与外设间的数据交换,TI提供了内含交换结构的EDMA3.0—— 一种特别的数据交换方式。同时,在接口方面,TMS320C6472具备SPI接口、Utopia光口、串行高速I/O(SRIO)、DDR2、千兆以太网、主机端口接口(HPI)以及Rapid IO接口等。Rapid IO是一个高速的、可以做集联的接口,通过Rapid IO可以将多个DSP集合成DSP阵列,当出现更高的应用需求时,即可通过Rapid IO接口,把多片TMS320C6472集联在一起。正是借助共享的L2存储器和带交换功能的EDMA3.0,TMS320C6472的6个核在运算和开发过程中实现了良好地协同工作。

小空间,低成本

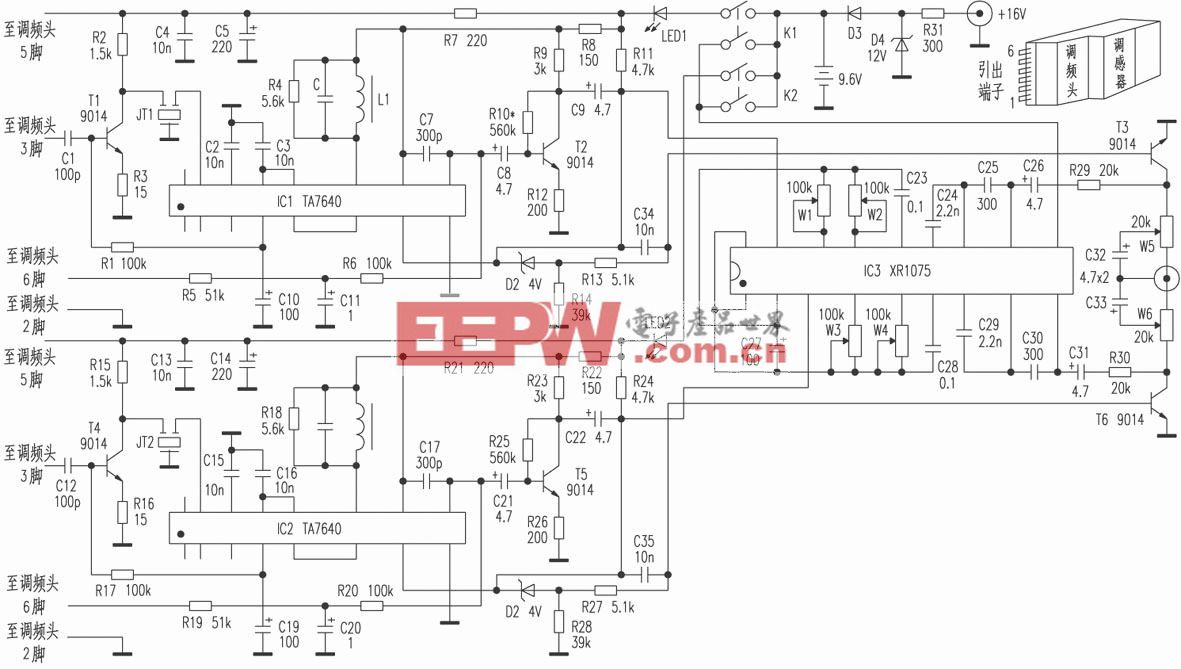

与前期推出的高性能定点DSP C6415对比,具备同样性能的C6472成本只是前者的1/3,并节省了80%的板级空间。郑小龙说:“仅仅从成本角度来说,6颗C6415芯片的成本约为450美元,C6472则仅需140美元。”

此外,为了降低对于开发成本的忧虑,TI同步推出了售价仅为349美元的小型开发系统TMDXEVM6472,它包含开发工具、支持还有代码兼容。同时,为了加快在多核器件上优化运行代码的编写进程,TI 针对 C6472 提供了广泛的技术支持,包括:功能稳健的软件库以及第三方产业环境等。

TMS320C6472可用于支持能够驱动多通道、要求最高性能密度以及设计人员需要实现复杂功能的应用领域。采用TMS320C6472的众多应用都无需任何外部存储器,从而不仅能够进一步改进功率曲线,同时还能大幅降低器件成本。这些器件可理想适用于广泛的应用领域,如高端工业应用、测试测量、通信、医疗影像、高端成像及视频,以及刀片服务器等。

在谈到TI高端DSP 的发展规划时,郑小龙先生表示,TI仍将并行发展单核与多核两大主线,在单核方面,将进一步尝试突破其性能时钟;在多核方面,则将着重发展性能优化与电源优化的多核技术,前者更倾向于性能的提升,面向医疗等领域,后者则更注意功耗的降低。此外,还将推出双核的新一代产品,满足部分客户的个性化及系统优化需求。

TMS320C6474架构图

评论