基于CPLD的LED点阵显示控制器设计

场可编程器件(FPGA和CPLD)等ISP器件无须编程器,利用器件厂商提供的编程套件,采用自顶而下的模块化设计方法,使用原理图或硬件描述语言(VHDL)等方法来描述电路逻辑关系,可直接对安装在目标板上的器件编程。它易学、易用、简化了系统设计,减小了系统规模,缩短设计周期,降低了生产设计成本,从而给电子产品的设计和生产带来了革命性的变化。

本文引用地址:https://www.eepw.com.cn/article/248954.htm1、系统结构及工作原理

LED点阵显示控制的传统方式是采用单片机或系统机作为CPU来实现,当系统显示的信息比较多时,由于单片机的输入/输出端口(I/O)有限,采用此方式的成本将大大增加,系统和程序的设计难度也急剧增加;而且,当系统完成后修改、改变显示方式或扩展时,所需改动的地方比较大,甚至有可能需要重新设计;另外,在以显示为主的系统中,单片机的运算和控制等主要功能的利用率很低,单片机的优势得不到发挥,相当于很大得资源浪费。如果采用现场可编程逻辑器件作为CPU来设计控制器,选择合适的器件,利用器件

丰富的I/O口、内部逻辑和连线资源,采用自顶而下的模块化设计方法,可以方便地设计整个显示系统。

由于PLD器件的外围器件很少,且可以利用PLD的编程端口(可复用)进行在系统编程,使得系统的修改、显示方式的改变和扩展都变的非常简单、方便。

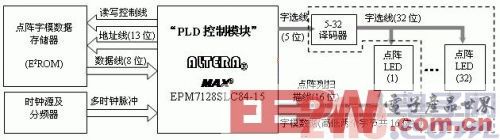

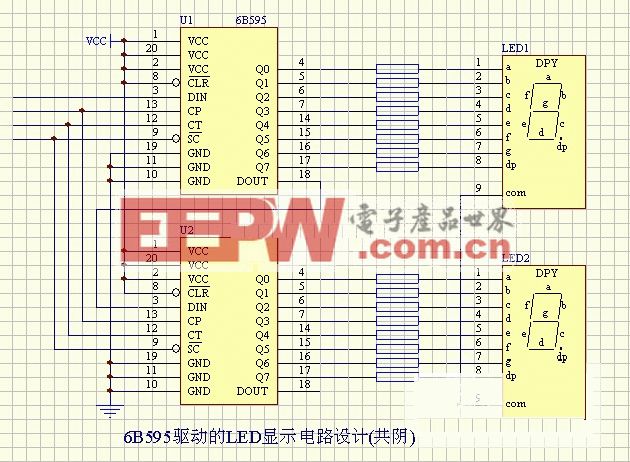

本系统采用单个16×16LED点阵逐列左移(或右移)显示汉字或字符,需显示汉字或符号的16×16点阵字模已经存放在字模存储器中。显示控制器由复杂可编程逻辑器件(CPLD)EPM7128SLC84-15来实现,系统组成原理框图如图1所示。

系统原理是PLD控制模块首先产生点阵字模地址,并从存储器读出数据存放在16位寄存器中,然后输出到LED点阵的列,同时对点阵列循环扫描以动态显示数据,当需要显示数据字模的列和被选中的列能够协调配合起来,就可以正确显示汉字或符号。

图1 点阵显示控制器原理框图

2、控制器设计及工作原理

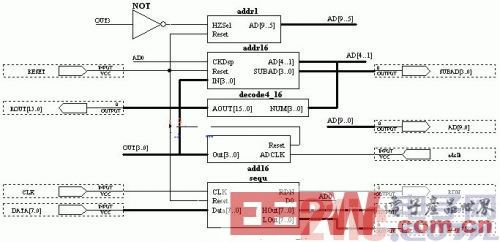

从框图中可以看出,系统的关键在于控制器的设计。LED点阵显示数据地址的产生、点阵列扫描和需显示数据的配合以及点阵显示方式控制的实现都必须由控制器来实现。对单个16×16LED点阵显示控制器进行设计的顶层逻辑原理图如图2所示。

图2 控制器顶层电路原理图

原理图中包含5个模块,其中sequ模块产生读信号RDN和10位地址线(AD[9..0])中的最低位地址AD0,AD0和其它模块产生的地址配合,通过8位数据线(DATA[7..0])从存储器读出列高字节(AD0=1时)和低字节(AD0=0时),由于16×16点阵字模数据为32个字节,每列含两个字节即16位,它由HOUT[7..0]和LOUT[7..0] 来构成;模块add16由adclk提供一个慢时钟构成16进制计数器,它的输出送给addr16模块,为变模计数器addr16提供一个模,通过模的规律变化以控制点阵按照左移或右移等显示方式进行显示;模块decode4_16是一个4—16译码器,其输出ROUT[15..0]连接到LED点阵的列,可选中16×16LED点阵的某列,并显示sequ模块输出的点阵高低字节(字模)数据;模块addr16为点阵显示控制的核心,为了实现点阵汉字从右到左逐列移动显示,它由add16模块提供的模,在addr16内部构成两个变模计数器,其中一个用来产生读字模数据的地址AD[4..1],另外一个产生16×16LED点阵列扫描选择地址SUABAD[3..0],列扫描选择地址由decode4_16译码后输出;模块addr1为字选择计数器,其输出可以控制多块LED显示器的显示及其显示方式。

控制核心模块addr16采用AHDL语言设计,在开发软件MAX+plus Ⅱ10.2中实现,程序如下所示。

SUBDESIGN addr16

(

ckdsp,reset,in[3..0]:INPUT;

ad[4..1],subad[3..0]:OUTPUT;

)

VARIABLE

reg1[3..0]: DFF;

reg2[3..0]: DFF;

reg3[3..0]: DFF;

BEGIN

reg1[].clk=ckdsp;

reg1[].clrn=reset;

reg2[].clk=ckdsp;

reg2[].clrn=reset;

reg3[].clk=!ckdsp;

reg3[].clrn=reset;

reg2[].d=15-in[];

if reg1[].q>=in[] then

reg1[].d=0;

else

reg1[].d=reg1[].q+1;

end if;

ad[]=reg1[];

reg3[].d=reg1[].q+reg2[].q;

subad[]=reg3[].q;

END;

为了实现字符由右到左逐列移动显示,模块addr16内部设计了两个由add16控制的变模加法计数器,其中一个输出为ad[4..1](4位地址线),另一个输出为subad[3..0](列扫描控制线)。

从程序可以看出,当模输入in[3..0]=0时,ad[4..1]=0,而subad[3..0]=15,此时ad[9..5]亦等于零,AD0 在0和1间变化,即读出第一个字符的第一列并显示在LED的第16列;当模输入in[3..0]=1时,在记数脉冲AD0的作用下,ad[4..1]和 subad[3..0]都为二进制加法计数器,但ad[4..1]由0加到1返回到0,同时subad[3..0]由14加到15返回到14,此时 ad[9..5]仍然等于零,AD0在0和1间变化,即读出第一个字符的第一、二列并显示在LED的第15、16列…由此类推,可见当模块add16的加法记数输出由0变到15时,LED点阵字符将由左到右逐列移动显示。

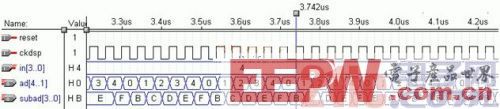

以上程序在MAX+plusⅡ10.2上仿真验证结果如图3所示。由仿真结果可以看到,由计数模控制输入in[3..0]控制的两个变模计数器输出ad[4..1]和subad[3..0]的结果正确无误。

图3 addr16模块仿真时序图

在设计中,应注意模块sequ的记数时钟CLK频率的选择应远远大于模块add16的记数时钟adclk的频率,addr16的记数时钟为地址最低位AD0,字选择计数器的时钟脉冲为16进制模块add16的最高位OUT3。这样,ad[4..1]和subad[3..0]同步变化的足够快,在点阵 LED上可以看到完整的字符,并当add16记数到15产生进位返回到0时,字选择模块addr1获得一个记数脉冲并加1(上升沿触发),此后将显示下一个字符。

3、系统扩展

以上为显示单个字符系统,若要同时显示多个字符时,可以按照图1加入虚线框内部分,并且模块addr1设计成addr16的格式,把AD4作为 addr1的记数脉冲即可。按照EPM7128SLC84—15的资源(64个I/O口,2个全局时钟,1个全局复位和5个可复用专用端口,5000个等效逻辑门,192个内部寄存器),若不外部扩展译码器,可以有效控制约16个字符的显示;而采用外部译码器时,可以控制的字符数将大大增加,但须注意时钟 CLK的频率需要提高,以视觉不能看到整个字符的闪烁为基准。

4、结论

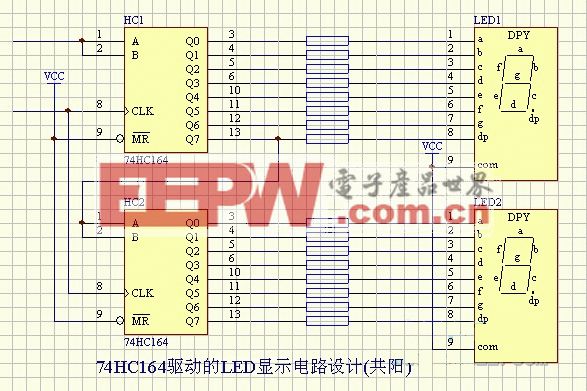

以上点阵字符显示系统在开发软件MAX+plusⅡ10.2上经仿真验证无误,并且已经成功地应用在煤矿电力监控系统的大屏幕显示中。另外,由于器件含有丰富的可编程连线资源,当系统显示方式和显示字符个数变化时,只需要通过开发工具修改控制器的控制逻辑和连接关系,再将修改完成的程序通过下载电缆下载到器件即可,而电路板可以不做任何改动,可见,系统的维护和修改是极其方便和容易的。当然,由于CLPD的驱动能力有限,当点阵LED显示亮度不够时,需要添加LED驱动电路以得到合适的LED显示亮度。

led显示器相关文章:led显示器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论