一种基于SOPC技术的便携式定位系统设计

随着GPS(Global Positioning System)全球定位系统的不断改进,应用领域正在不断地开拓,目前已遍及国民经济各种部门,并开始逐步深入人们的日常生活。当前基于GPS定位产品体积一般较大,且处理核心大多采用单片机,单板机等,产品开发周期长,开发成本高,产品升级不方便,生命周期短。

超大规模集成电路技术的发展,尤其是PLD和FPGA技术的发展,使得在一块可编程芯片上实现整个的嵌入式系统成为可能。SOPC(System on a programmable chip)技术将CPU,存储器,I/O接口等系统设计所必须的模块集成在一片FPGA上,具有设计灵活,可裁减、可扩充、可升级、软硬件在系统可编程的功能[1]。

本文设计了一种基于SOPC技术的便携式定位系统,并针对GPS在城市高楼和地下停车场等地方容易出现定位盲区的问题,提出采用GPS/数字指南针组合定位的解决方案。本文首先介绍了系统组成和硬件实现,再对软件开发作了详细分析,并给出了源程序,最后对试验样机进行了试验,验证了系统的可行性。

1 系统基本结构

基于NIOSⅡ的便携式组合定位系统由两部分组成:接收终端和监控中心。接收终端接收GPS/数字指南针组合定位信号,并通过GPRS模块发往监控中心,监控中心将接收到的组合定位信号进行数据融合,采用基于模糊模式识别技术的地图匹配法,借助GIS电子地图库中的高精度道路信息作为分类模板来进行模式识别,根据识别结果来提高GPS接收数据的定位精度,实现数据与电子地图的实时匹配,实时地显示接收终端佩戴者所在的位置,授权用户也可以通过Internet随时随地查看终端佩戴者的位置。一旦发生紧急情况,终端佩带者可以触发终端上的报警按钮,由监控中心实时进行相应处理。

2 接收终端硬件设计

系统接收终端硬件由一块FPGA芯片和GPS模块,GPRS模块,数字指南针模块,报警模块等组成,在FPGA芯片中主要实现NIOSⅡ软核处理器,片上存储器和数字接口电路的功能。

NIOSⅡ是Altera公司推出的32位RISC嵌入式处理器,能和用户逻辑相结合,编程至Altera FPGA中。处理器具有32位指令集,32位数据通道和可配置的指令及数据缓冲,实现成本低,在FPGA中实现成本只要35美分,灵活性大,采用软核形式,具有完全的可定制特性,设计人员可根据实际需求在多种系统设置组合中进行选择,达到性能、特性和成本最优化,具有超过200DMIP的性能[2]。可以通过下载硬件配置文件到FPGA来实现更新,非常方便。

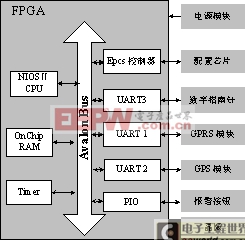

根据系统的功能要求和NIOS II软核处理器的高度可配置性,在硬件开发工具SOPC Builde定制的NIOS II软核处理器系统如图1所示,在一块Altera EP1C12Q240C8 FPGA上实现了NIOSⅡ软核CPU,OnChip RAM,Timer,UART,Epcs controller等模块,NIOSⅡ软核CPU和其它IP模块之间通过Avalon片上总线相连,该总线规定了主部件和从部件之间进行连接的端口和通信的时序。

图1定制的NIOSⅡ处理器系统

UART串口通信模块用于NIOSⅡ处理器和外部的通信,本系统通过串口采集GPS和数字指南针的定位信号,并通过串口将定位信号和报警信号发给GPRS模块发往监控中心。On Chip RAM为系统提高片上存储单元,CY1C12Q240C8提供了239,616 bits的RAM单元,系统无需扩展外部存储器。Epcs controller模块用于系统上电时,控制硬件配置文件和程序从串行配置芯片下载到FPGA中。Timer定时器模块提供系统定时中断,报警模块由一个按钮组成,终端佩带者遇到紧急情况时通过触发按钮向监控中心报警。电源模块给系统提供系统电源,晶振模块给系统提供系统时钟。

评论