SOI技术的优势及其制造技术

1 引 言

SOI是英文Silicon-On-Insulator的简称,指具有在绝缘衬底上再生长一层单晶硅薄,或者是单晶硅薄膜被绝缘层(通常是Sio2)从支撑的硅衬底中分开这样结构的材料。

最初人们开发研究SOI材料是为了代替 SOS(Silicon-On-Sapphire)( 注:绝缘衬底为蓝宝石)材料制作用于空间军事用途的抗辐射集成电路。由于发现薄膜SOI MOSFET具有极好的等比例缩小的性质,使得SOI技术在深亚微米VLSI中的应用中具有极大吸引力。目前SOI技术走向商业应用阶段,特别是应用在低压,低功耗电路[1-2〕,高频微波电路以及耐高温抗辐射电路[3]等。

本文通过比较SOI和体硅器件在寄生电容,闭锁效应,热载流子效应以及辐射效应等方面的差异,阐述了SOI的优越性。并介绍了SOI晶片的三种主流制造技术,以及其在微电子领域的发展趋势和存在的问题。

1.1 SOI的优越性[4,5,6,7]

SOI结构的器件比类似的体硅器件具有更多的优点,下面我们以CMOS为例对二者进行比较。

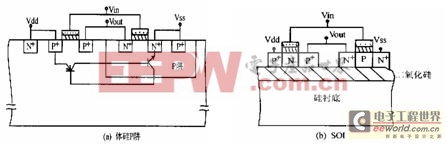

CMOS集成电路的基本单元是CMOS反相器,由一个NMOS和一个PMOS构成。由图一可知体硅的CMOS反相器中PMOS制作在N型衬底上,而NMOS制作在P阱中(P阱是在N型衬底上用离子注入技术特意制作的局部P型材料)。P阱将NMOS和PMOS相互隔离。而SOI CMOS中的PMOS管和NMOS管分别制作在SOI材料顶部薄Si层中,NMOS和PMOS是相互隔离的。由于体硅CMOS和SOI CMOS结构上的不同,因而它们在寄生电容,闩锁效应,热载流子效应和辐照特性等方面有很大的差异。

图1 CMOS反相器剖面图

2.1 寄生电容

NMOS和PMOS源漏扩散区与衬底之间的寄生电容随衬底掺杂浓度线性变化。随着器件尺寸缩小,为减小短沟道效应,衬底掺杂浓度必须适当提高,源漏结电容随之增大,结和沟道阻断区之间的寄生电容随之增加。这影响了电路运行速度,还增加电路的功耗。

在SOI电路中,结与衬底的寄生电容是隐埋的绝缘体电容。该电容正比于绝缘层Sio2的介电常数,Sio2的介电常数仅为Si的1/3。而且随着器件尺寸的缩小,隐埋Sio2层的厚度不需要按比例缩小,寄生电容不会增加。另外。SOI器件的其他寄生电容,如硅衬底和多晶硅层,金属互连线之间的电容也减少了。在VLSI向深亚微米方向发展时,寄生电容的降低将明显提高电路的速度。

2.2 闭锁效应

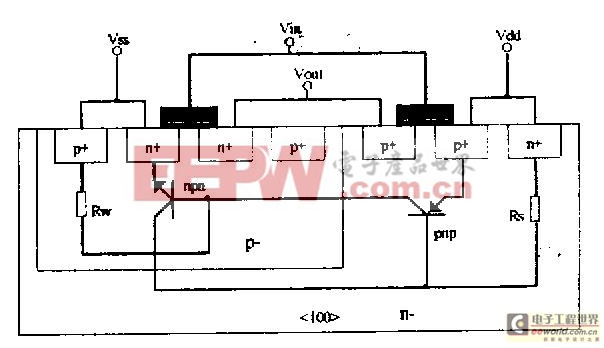

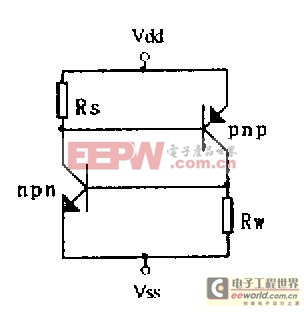

闭锁(Latch-up)效应又称可控硅效应,是体硅CMOS电路中的一个特有的问题。从图2所示的CMOS断面结构图上,可以看到存在纵向NPN横向PNP两个寄生双极晶体管,他们分别由衬底、阱和源漏结构成。若高掺杂区的内阻略而不记,那么这些寄生晶体管和Rw、Rs一起构成了图三所示的正反馈电路。当电流放大系数β1*β2>1,且两个晶体管的基极—发射极正向偏置,闭锁效应即可触发。

图2 体硅CMOS断面结构图

图3 等效电路

如果采用SOI结构,由于没有到衬底的导电通道。闭锁效应的纵向通路被切断。所以SOI具有很好的抗闭锁性。

2.3 热载流子效应

随着器件集成度的提高,尺寸的减小,衬底的掺杂浓度增加,而电源电压没有相应按比例降低,这使得沟道内的横向、纵向电场急剧增加,载流子在电场加速下成为热载流子(hot-carrier)。其中一部分注入到栅氧化层中,改变了氧化层界面内永久电荷的分布。从而引起跨导的减小、阈电压漂移和漏电流减少。当注入数目较多时,可以检测到栅电流的存在。

高能电子还通过碰撞电离产生电子——空穴对。在体硅器件中所产生的空穴流入衬底形成衬底电流。衬底电流与栅电流存在一定的关系,且器件寿命与栅氧化层中热电子注入数目有关。由栅氧化层热载流子退变所定义的器件寿命г与碰撞离化电流有关。在全耗尽SOI MOSFET中,M可通过漏端附近对撞离化系数的积分得到,且与漏电压和栅电压有关。器件寿命与放大因子有关。有关研究发现[1,5,6,7]全耗尽 SOI MOSFET中的热电子退变要比体硅弱,SOI的寿命更长可靠性更高。

2.4 辐射效应

在空间环境中,集成电路会受到核辐射。MOS器件是多子器件,抗中子辐射能力强,但对单粒子事件(SEU)、γ辐照相当敏感。

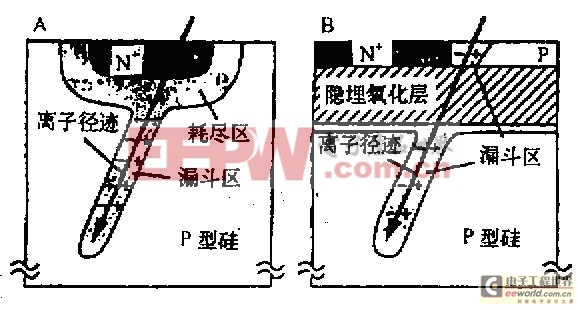

当一个载能粒子(如α粒子或重离子)入射到一个反偏的P-N结耗尽区及下面的体硅区时,沿着粒子运行轨迹,硅原子被电离,即产生电子—空穴对。这种轨迹的存在使其附近的P-N结耗尽层发生短时塌陷,并且使耗尽层电场的等位面变形,称为“漏斗”(见图4)。在体硅器件内,在电场作用下,电子将被耗尽层所收集,而空穴向下移动并产生衬底电流。这些电子使得所在电路节点处的逻辑状态发生反转,造成电路的软失效。而在SOI器件中,由于有源区和衬底之间存在着隐埋氧化层,所以衬底区内产生的电荷不会被SOI器件的结所收集,只有顶层膜内产生的电荷才能被收集,所以SOI器件具有抗软失效能力,产生单粒子事件的几率比体硅器件小的多。

图4 载能粒子在体硅和SOI中的射入

3 SOI的制造方法

形成SOI的方法很多,如深注入氧或氮到硅衬底、二氧化硅上多晶硅的激光(或电子束、红外等)退火再结晶、二氧化硅上多晶硅的石墨条等加热再结晶、多孔硅氧化、硅的横向外延、硅片键合及其减薄等。近年来应用最多发展,最成熟的是SIMOX技术、硅片键合[5, 8]、智能切割[6, 7],这三种技术有可能在VLSI中得到广泛应用。

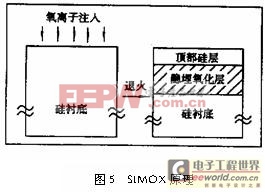

3.1 SIMOX技术

SIMOX (Separation by Implanted Oxygen)是目前制造SOI材料最可行的制造方法之一,其主要优势是制造的硅膜和隐埋层(BOX)均匀性好。这是因为氧离子注入是以晶片表面作为参考面,顶层硅膜、埋层Sio2退火时均能得到保角变换。

SIMOX的基本工艺包括:

(1)氧离子注入(剂量约为3×1017-2×1018)

(2)高温(1 3500C)热退火1-4h。

(3)晶片清洗(去掉表面微粒和沾污)

离子注入工艺对于SIMOX技术起着决定作用,它决定晶片的产量、成本、和初级质量参数。

在SIMOX技术进展方面,另外两个显著的进展表现在原位监控技术和晶片电学参数表征技术的日趋完善。最新的研究表明[9, 12],使用轻掺杂衬底,BOX厚度可降至50nm,而不影响电路和速度的功耗特性。因为SOI衬底中的寄生电容主要来自耗尽层几乎与BOX厚度无关。低的注入能量和注入剂量能降低晶片的沾污。薄的BOX层能减少短沟道效应,改善散热,提高抗总辐射剂量。所以低剂量、薄的隐埋氧化层(150-200nm)成了SIMOX SOI材料的发展趋势。

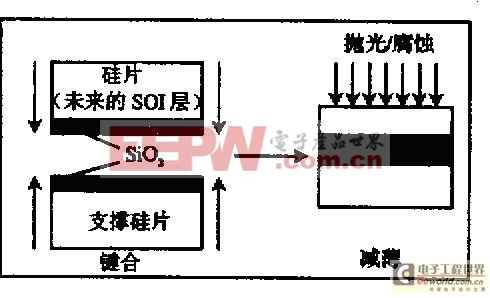

3.2 硅片键合技术(Bonded and Etch-back SOI)

硅片键合法的主要工艺过程是(图6):

图6 硅片键合技术原理

(1)把经过热氧化的两片硅片作亲水处理,然后重叠在一起,吸附在表面的羟基团在室温下受Van der wall力作用相互吸引,使两个硅片键合在一起,再经过适当的温度退火来增强界面键合程度。

(2)有源区硅层。利用机械研磨和(化学)抛光将其中一片减薄到1um,即形成SOI结构。

硅片键合技术成本较高,除了一些技术上的问题有待解决外,其面临的一个主要挑战是如何通过简化工艺步骤,提高设备产出能力等手段来降低成本。

3.3 智能切割技术(Smart---cut)

智能切割技术综合了SIMOX和硅片键合两种方法的优点,成功的解决了键合SOI中硅膜的减薄问题,可获得均匀性很好的顶层硅膜,且硅膜质量接近于体硅。另外,剥离下来的硅片又可以作为下一次键合的衬底,大大降低了成本。该技术是目前最受关注的SOI制备技术之一。

智能切割的独创性在于通过注H+并在加热的情况下形成气泡,使晶片在注入深度处发生断裂,达到减薄的目的。它涉及的化学反应式如下:

减合界面处 Si-OH +Si-OH→Si-O-Si+H2O

Si+ H2O→Sio2+ H2

加温时 Si-H +Si-H→Si-Si+ H2

智能切割主要包括四个步骤

(1)离子注入硅片A中。A上长有介电层如SiO2。典型的注入剂量为3.5×1016~1×1017

(2)对A和支撑片B进行RCA清洗,然后低温键合。B起到“加热板”的作用。

(3)两步热处理:1)400~600OC使A在H原子分布峰处剥离,其中一薄层单晶硅和支撑片B形成SOI结构(称Unibond SOI片)。2)(1 100OC氮气气氛下),目的是增强键合强度和恢复顶层硅膜的注入损伤。

(4)表面抛光。使粗糙度≤0.15um.

4 SOI技术存在的问题和挑战

SOI CMOS 是全介质隔离的、无闩锁效应、有源区面积小、寄生电容小、泄漏电流小、能工作在各种恶劣环境中,因此SOI CMOS具有优越的性能,在抗辐照电路、耐高温电路、亚微米及深亚微米VLSI、低压低功耗电路及三维集成电路中有着广泛的应用。

虽然SOI技术有着诸多体硅不可比拟的优点,而且人们相继制备出性能良好的SOI器件和电路。但SOI仍没有从实验室解放出来实现大规模生产。缺乏低成本高质量的SOI衬底材料和SOI IC的成品率较低是SOI技术成为主流的主要障碍。

SOI在材料的选择上非常严格,用于制作MOS管的硅必须是结晶状态的硅,而使用的绝缘体(Sio2)必须不含一丝杂质,否则无法阻止电子的流失,从而使SOI技术失去意义。

另外,到目前为止,人们对SOI的浮体效应以及浮体效应导致的阈电压的浮动、记忆效应、迟滞效应等对实际电路的影响和如何克服认识的还不是很清楚。

就制造技术而言SIMOX材料最新的趋势是低剂量,虽可降低成本但埋氧的厚度限制在80-100nm内。另外SIMOX面临的最大的问题是要使用非标准的仪器设备和高于1300OC的热处理过程。这使得制备大面积(>300mm)SIMOX材料较为困难。键合(Bonded)技术虽可以得到接近硅的高质量硅膜,且能得到较大的埋氧厚度和硅膜厚度。但硅膜的减薄和成本的高昂是该技术发展的障碍。智能切割技术虽然比较完美。可是目前控制工艺还不完善。

参考文献

〔1〕 EimoriJ,OashiT,Approaches to extra low voltage DRAM operation by SOI-DRAM.IEEE Trans Elec Dev,1998;45(5);1000-10009

〔2〕 Colinge J P,Chen J,A low voltage,low-power microwave SOI MOSFET, Proc IEEE Int SOI Cont 1996,128-129

〔3〕 Massengill L W,Kerns D V,Single-event charge Enhancement in soi devies,IEEE Elec Dev lett,1990;11;98-99

〔4〕 CMOS:From Bluk to SOI http://www.ibis.com

〔5〕 伍志刚,凌荣堂 SOI技术—21世纪的硅集成技术,微电子学31(1)2001;2

〔6〕 张廷庆,SOI—21世纪的硅集成电路技术 电子元器件应用3(3)2001;3

〔7〕 J P Colinge Silicon-on-insulutor Technolgy material to VLSI.Kluwer Academic pub 1991 中译本:武国英等译 科学出版社 1993。

〔8〕 吴东平,黄宜平,竺士炀 晶片键合技术及其在微电子学中的应用,微电子学29(1) 1999;2

〔9〕 罗南林,吴福根, SOI技术及其最新进展 广东工业大学学报 16(3)1999;9

〔10〕任学民,SOI晶片制造技术及其应用前景,半导体技术24(3) 1999;6

〔11〕储佳等 一种新的SOI技术—智能切割 半导体技术 26(1) 2001;1

〔12〕郑望等 低剂量SIMOX圆片表层硅缺陷密度 半导体学报 22(7) 2001;7

〔13〕Han Wei-hua and Yu Jin-zhong Modeling Thermodynamics of Smart-cut process 半导体学报,22(7) 2001;7

〔14〕徐文华,张天义等 SOI技术的机遇和挑战 电子器件 24(1)2001;3

作者介绍 崔帅(1978-)男 ,硕士研究生,毕业于河北大学物理系,目前感兴趣的方向 SOI技术、抗辐射加固、器件可靠性。

评论