基于TMS320F240 DSP的激励器控制系统

1 引言

激励器是为发射机提供高精度、高稳定载波的器件。目前许多激励器的控制系统因其核心器件(如MCS-51)速度和精度的限制,存在频率同步精度低,校频速度慢等问题。DSP可实现复杂控制规律、抗干扰能力强、性价比高,是实现控制激励器输出精密载波的理想选择。这里介绍以DSP器件TMS320F240为核心的激励器控制系统设计与实现。

2 控制系统原理

该激励器内5 MHz压控晶振的输出不能满足频差小于每天0.01 Hz的实际稳定性需求,因此需用标准的频率信号(简称标频)校正其晶振输出的频率(简称校频)。要提高输出频率精度,首先要处理好标频,达到其频率准确度高、抖动小、信号输出稳定、且满足幅度要求。

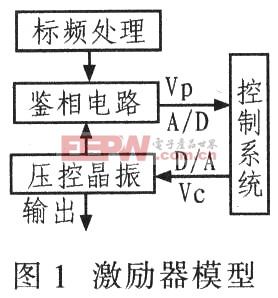

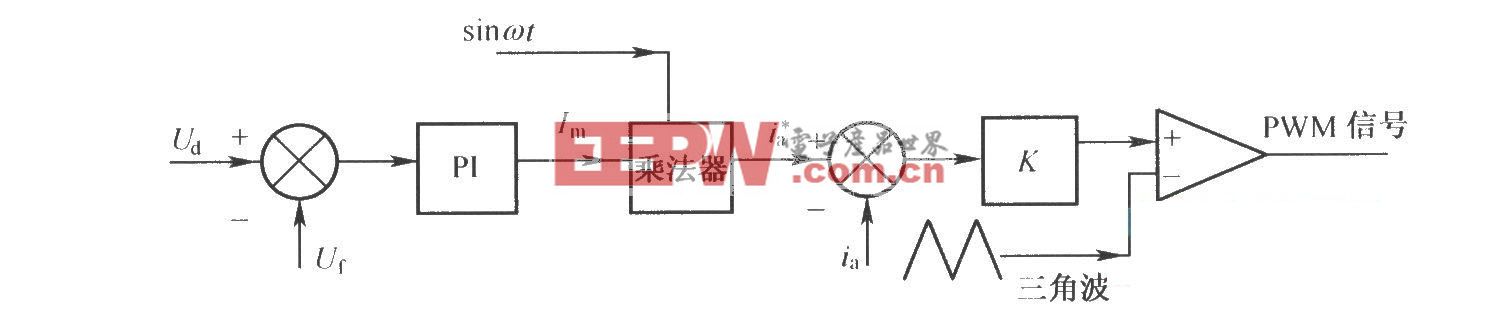

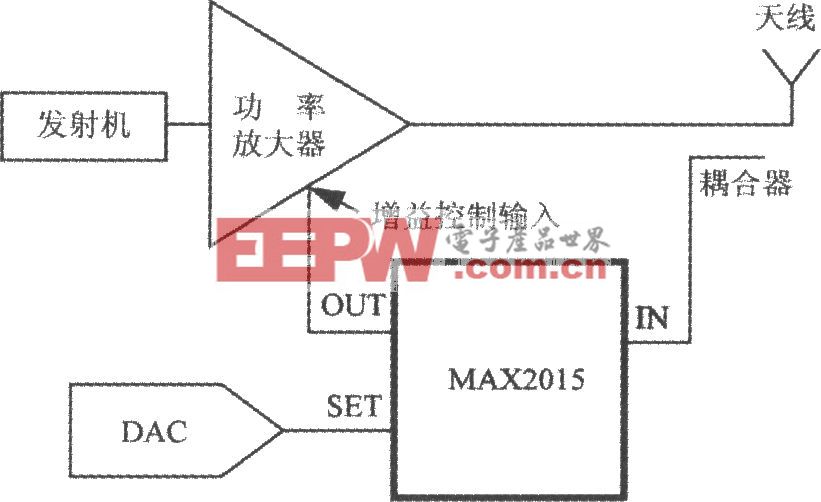

图l为激励器模型。该控制系统插在鉴相电路板与5 MHz压控晶振(VCX0)间,与二者组成锁相环路。锁相环路以彩色电视副载波信号(4.43 MHz)为标频,定时校对压控晶振的频率。鉴相电路输出包含晶振频差的电压Vp。校频过程中控制系统对Vp进行数据采集和数据处理,并使输出控制电压Vc加到压控晶振的电压控制端,调整各自振荡频率,使其与标频源的准确度一致。校频完成后,系统保持校频处理后的控制电压,压控晶振输出校准后的频率。

3 控制系统设计

3.1 硬件电路设计

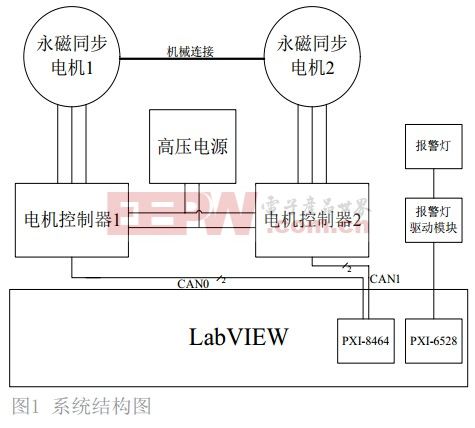

该控制系统的硬件电路主要由TMS320F240、复位电路、12位A/D转换器与D/A转换器接口电路、键盘与LED显示接口电路、鉴相与输出的状态检测指示、微型打印机并行接口以及系统与PC机通信的串行接口等组成。其结构如图2所示。

3.1.1 TMS320F240简介

根据该系统指标和任务要求,以及系统的性能和成本,TMS320F240采用高性能的DSP内核和微处理器的片内外围设备完全满足该控制系统设计。TMS320F240是传统的微控制单元(MCU)和昂贵多片设计的一种廉价替代产品,每秒2千万条指令的处理速度,以及丰富的硬件接口资源,使其提供远远超过传统的16位微控制器和微处理器的性能。

3.1.2 MD转换接口设计

根据该系统的实际功能需求,考虑到MD转换器的性价比因素,选用MAXIM公司的MAX1296。A/D转换器的接口设计中应注意以下关键问题:

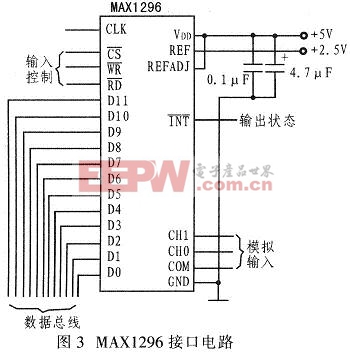

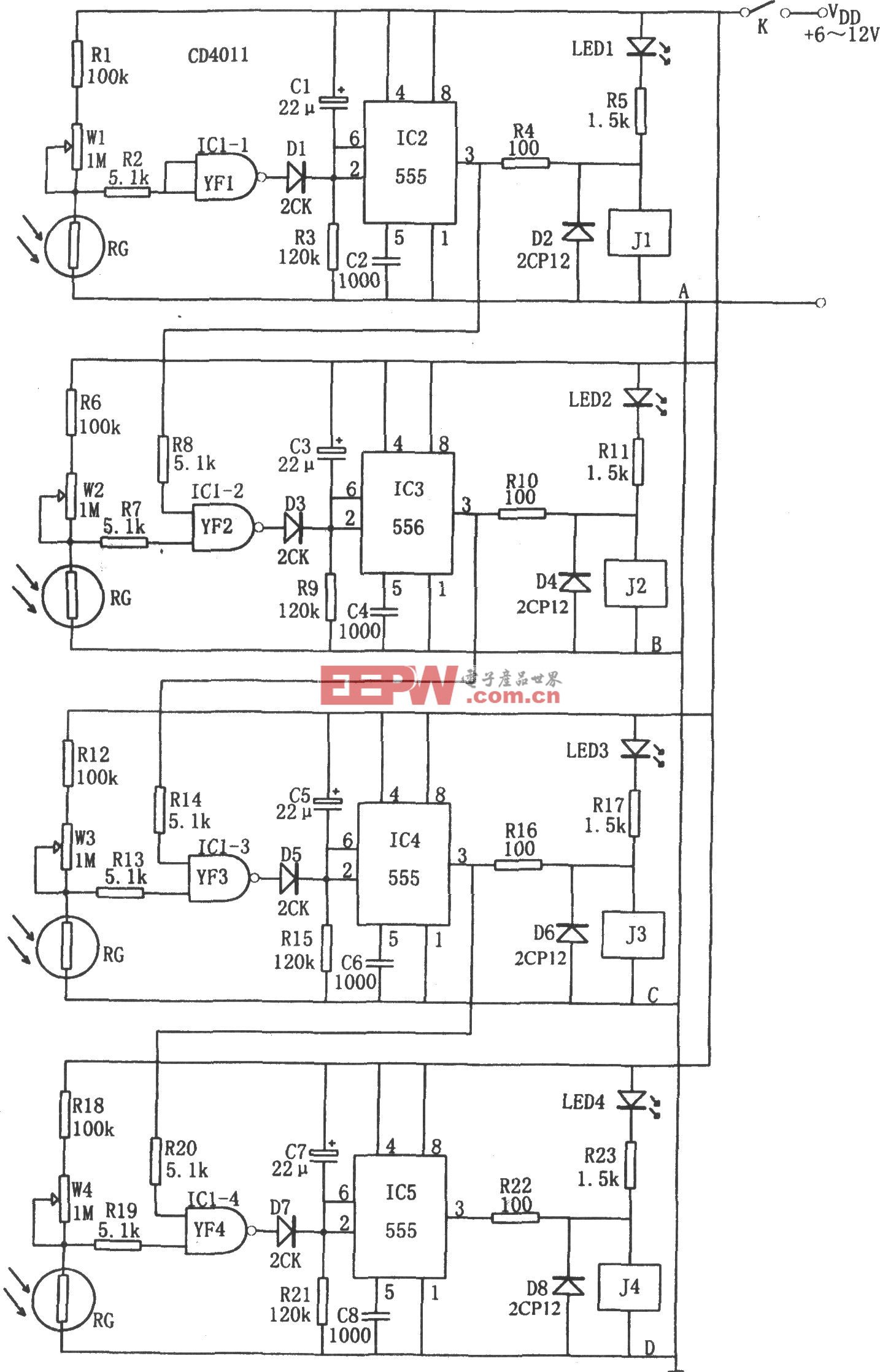

(1)MAX1296输出端与DSP的连接 A/D转换器分为内部含有和不含输出锁存器两种类型,后者通过锁存器或I/O接口与CPU相连;而前者则直接与CPU相连,本系统采用内部含有输出锁存器的MAX1296。图3为其接口电路。

(2)MAX1296的启动方式 A/D转换器需外加启动信号才能开始工作,具有脉冲和电平两种启动方式。MAX1296是脉冲启动转换器。只要在A/D转换器的启动转换输入引脚加肩动脉冲即可启动A/D转换器。

3.1. 3 其他硬件电路设计

系统处理后的控制电压值通过RC-232接口传到PC机内,以供维护人员参考;并可直接送入微型打印机。若鉴相和输出偏离过大,则系统告警指示,维护人员通过键盘输入经验电压值控制晶振。

3.2 软件程序设计

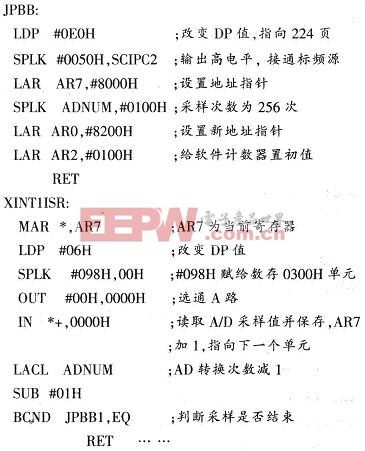

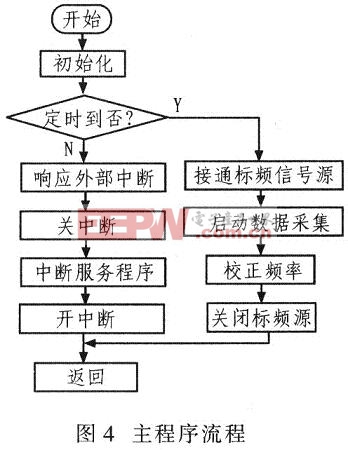

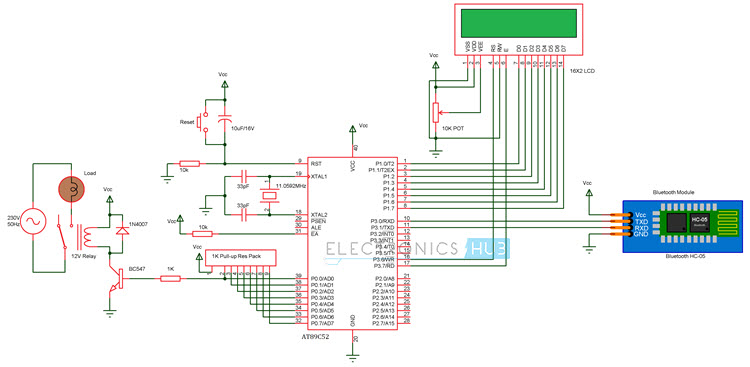

TMS320F240具有丰富的汇编指令系统,侧重于数字运算、信号处理以及高速测控等通用目的的应用。该控制系统在软件设计中用到外中断、软件定时器中断、模数转换中断等。具体包括主程序及键盘处理、时钟处理、定时校频等子程序。主程序中,CPU首先初始化时钟、工作状态显示、输出控制电压和有关寄存器等。若到达定时时间,则执行定时校频子程序,否则循环执行主程序。图4为其主程序流程。校频子程序的部分程序段如下:

3.3 抗干扰设计

由于本激励器控制系统所处环境具有强磁强电干扰,故在系统的软、硬件设计方面尽量考虑抗干扰,主要表现:(1)软件设计采用抗脉冲干扰平均值法、算术平均值滤波法处理采集的数据;(2)系统+5 V电源由一个单独的220 V降压变压器提取,以保证不受其他部件拔插和工作影响;(3)为确保A/D转换器和D/A转换器的转换精度,MAX1296和MAX530的参考电压均由精密基准源提供;(4)在MAX232E和TMS320F240之间采用光电隔离措施,二者之间使用光电耦合器,以避免干扰而对信号进行隔离传输;而且MAX232E的+5 V电源和其他电源也不能共用。

4 结束语

经过初步软硬件调试,本控制系统大大加快了激励器校频的速度,使其校频精度达到了指标要求(频差远小于每天0.01 Hz,校频精度优于5x10-10),提高其强磁强电环境下的抗干扰能力,各项功能均达到预期设计目的。

评论