基于CY7C68013的USB2.0数据传输模块设计

1 引 言

通用串行总线(USB)[1]是一种电缆总线。它支持主计算机与许多可同时访问的外设之间进行数据交换。使外设的连接具有单一化、即插即用、热插拔等特点,已经成为个人笔记本电脑和台式机的标准配置接口。USB支持3种传输速率:1.5Mb/s的低速传输、12Mb/s的全速传输、480Mb/s的高速传输。Cypress公司的EZ-USB FX2是一款集成 USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强的8051微控 制器和可编程的外围接口。每条指令占四个时钟周期,在48M晶振下工作时,单指令周 期为83.3ns,执行速度远快于标准的8051单片机。本文的数据传输模块采用CY7C68013 高速芯片设计的USB接口可以实现外部的存储测试电路数据的快速下载,并且上传至计 算机保存,显示,处理。文中重点介绍CY7C68013的GPIF接口功能及其在设计中的实现机理。

2 硬件连接设计

2.1系统连接框图及硬件各部分功能

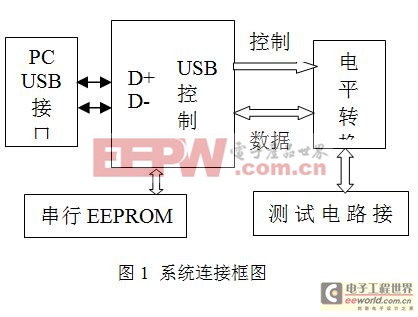

系统的连接框图如下图1所示:主要有计算机主机USB接口,程序存储EEPROM,内置MCU的USB接口芯片,电平转换部分组成。

硬件各部分功能:

设备接口:实现模块与测试电路的连接;

电平转换:单片机的输出和工作电压为3.3V的电压值,而设备的电压是3.3~5V之间,电平转换器件实现电压值的匹配;

USB总线控制器:采用CY7C68013接口芯片的GPI接口模式完成控制信号的发送和16bit宽度数据的读取;

串行EEPROM:存储单片机固件,并被下载到单片机。

2.2硬件部分工作过程

硬件工作过程:

数据传输中核心器件是CY7C68013控制器芯片,主要完成USB的事务处理和单片机的控制功能。系统采用总线供电模式,数据传输模块连接到计算机后,上电复位后,USB功能设备以全速的模式进行设备的识别并枚举。设计中将程序存储到串行EEPROM中,主芯片首先检测I2C总线上的EEPROM,判断其首字节是0xC2,下载固件和USB的描述符标装入到自身的RAM中执行,并且根据信息设置定义设备,完成了重枚举。 CY7C68013包含8.5KB的片上RAM,可以用于“软配置”,4KB的FIFO存储器可以给4个端点共享。实现数据的高速读取和传输,根据实际的需要,设计中配置了端点2采用三缓冲,使用3KB,端点4采用双缓冲使用1KB。

采用GPIF主机模式,EZ-USB FX2由软件编程输出读写控制波形,FD[15:0]双向数据总线12位与外部测试电路的静态存储器(SRAM)的相连,CTL[5:0]输出可编程控制信号,如SRAM的读写选通信号等。数据在GPIF控制下读入到CY7C68013后,在软件的配置下,完成1024字节的最大封包,输入计算机,由主机端的主控制器的串行接口引擎完成数据流串行化和解码。

评论