PXI模块触发总线接口的CPLD实现

pxi触发接口实现原理图

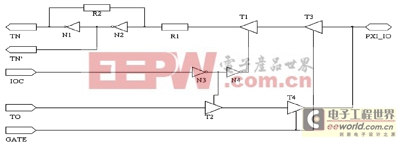

这里只给出一路触发总线实现的原理图,由于8路触发总线之间是独立工作的,因此,每一路都可以用同样的原理来实现,只是实际应用中,8路信号可以共用一些控制线而已。一路触发总线接口的原理如图1所示。

图1 触发总线接口的原理

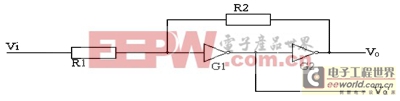

图1所示,由n1、n2、r1、r2组成了门电路施密特触发器,其原理图如图2所示。

图2 门电路施密特触发器的原理

图2所示,vi为触发器输入端,vo为输出端,vo为反相输出端口,g1、g2为两个反相器,其阈值电压vth=0.5vdd,且电阻r1r2,则电路状态发生转换时其正向阈值电压为vt+=(1+r1/r2)vth,负向阈值电压为vt-=(1-r1/r2)vth,正向阈值电压与负向阈值电压的差就称为回差电压,即δvt=vt+-vt-=2r1/r2 vth。

图1中,由t1、t2、n3和n4构成输入/输出控制部分,当ioc=1时,t1导通,t2截止,接口工作在输入状态,由别的模块送来的触发信号送入施密特触发器进行触发;当ioc=0时,t1截止,t2导通,接口工作在输出状态,触发信号通过本接口输出送到别的模块进行触发同步。

图1中,由t3和t4组成了一个三态输入/输出门,当系统上电复位时,gate输入低电平,两个三态门均处于高阻态,直到复位结束,由软件控制gate信号线变为高电平,三态门导通,接口处于正常的输入/输出状态。

该触发总线接口可以通过对cpld器件进行编程来实现,直接使用原理图方式输入。为了满足如上所述定则2中关于i/o缓冲器直流特性的要求,这里选用5v供电电源的cpld芯片。另外,由于电阻元件在cpld中不容易实现,可以采用外接电阻的方法,这也为选择电阻参数提供了更多的自由。

评论