HDTV接收机中Viterbi译码器的FPGA实现

3 译码器的性能

本文是在软件仿真的基础上,结合硬件实现的可行性和COFDM传输系统中的高数据率的实际情况,权衡资源占有和速度的矛盾进行的一种优化设计。

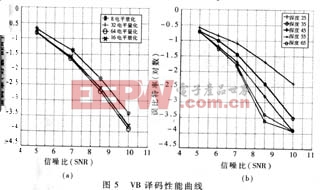

3.1 译码性能的软件仿真

软判决译码器的输入信息是经软判决量化后的数据。但量化的电平数与码元的可信度有直接的关系,量化电平越多,则越能精确地接近似然函数,越能准确反映接收码元的可信度,从而使译码器的译码性能更接近最大似然译码。但随着量化电平数目的增多,译码的复杂性也很快增长,实现的难度也随之加大。

图5a用MTLAB仿真得出了量化电平数对译码性能的影响。从波形可以看出,在16电平以上(32、64电平)量化时,误码与信噪比的性能曲线很接近,而相对于后两种量化来讲,16电平的FPGA电路实现要方便得多。因此本设计采用4比特量化。

在FPGA实现译码的过程中,译码深度是另外一个重要的决定译码性能的参数。图5b是仿真得到的在采用16电平量化时,对应不同深度下误码率与信噪比的关系。可以看出,当译码深度大于55时,SNR基本不再增加。BER=10-3时,深度为55的译码较45有0.65dB的增益。但从资源的占有程度来讲,前者却要多用640个逻辑单元。本设计采用的译码深度为45。

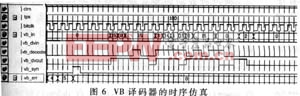

3.2 VB译码器的电路性能

基于上述分析,通过大量的电路和软件仿真,用FPGA方法完成了用于HDTV COFDM传输系统中的VB译码器的设计。通过用Tektronix TLA 700逻辑分析仪(数据深度为512K字节)调试,将采集到的每组可达520K字节的数据用软件仿真进行验证,确保在无扰信道情况下误码率为零,并在测试过程中验证了该译码电路具有的以下性能:

1适用于高速率系统,电路最高工作时钟可达70MHz,整个电路占用逻辑单元为7620个。同时不占RAM和ROM单元,为同一片内的其它电路模块节省了宝贵的共享内存资源。

2主码率为1/2,同时在不增加电路复杂性的情况下,可以对2/3,3/4,5/6,6/7,7/8等多种码率的数据进行译码。

3可自动实现译码同步和BER监控。

4采用并行电路设计,使电路在高时钟情况下可以稳定工作。

5 采用FPGA技术,易于修改电路内部参数,软判决可以兼容硬判决。通过内部参数的变化可以满足不同约束长度(7、9等)译码的要求。

图6给出了在FPGA电路的时序仿真波形。其中TPS为系统通过传输参数信令提供的码率信息。共有1/2、2/3、3/4、5/6、7/8等多种码率信息。电路工作时钟bitclk根据COFDM传输系统的要求为60MHz。Vb_in为4-bit量化后的软判决信息,译码输出串行比特流,并标注有数据有效和是否同步的标志。Vb_err用来监控误码,向电路发出提示信息,使电路始终工作在同步态。

本文的FPGA实现是基于Altera公司Quartus和MaxplusII电路仿真环境和该公司APEXTM EP20K600EBC652-1XES系列芯片来完成的。应用于高清晰度数字电视COFDM传输系统的接收机机顶盒的设计中,经过性能测试,达到了系统指标要求。同时,该设计也为HDTV机顶盒的ASIC设计奠定了良好的基础。

评论