HDTV接收机中Viterbi译码器的FPGA实现

2.1 译码器的整体实现方案

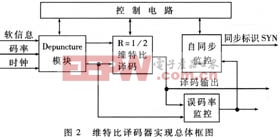

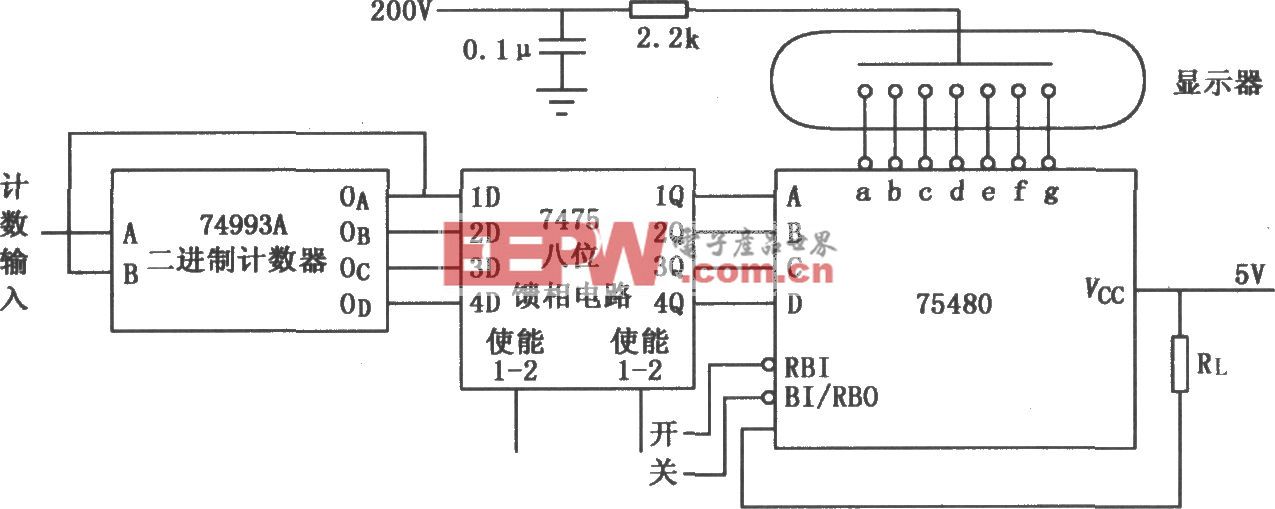

译码器的整体方案如图2所示。

发端的数据经由信道传输过来,经过同步和信道估计,根据CSI信息对数据进行维特比量化,将量化后的信息解内交织后送入维特比解码单元。

接收到前端的码字后,首先须在发端的删除位置上填充特定的虚假码元,这一功能由Depuncture单元来完成。并由该单元产生量度计算禁止脉冲,送入主译码器,使译码器在译码时禁止对这些码元作量度计算。

主译码器的译码输出送到误码率监控单元,通过对误码率的统计来判定数据是否为同步接收,同时将该信息送入自同步监控单元,以供调整同步使用。当整个译码系统同步后,将输出一同步标识,表示系统已经同步,同时通过同步单元维持同步态。

2.2 译码器分模块的实现

2.2.1 R=1/2的维特比译码模块

根据上述VB算法,对于一个软判决译码器,应具备以下几部分:

(1)度量值寄存器:用来存储各路径的度量值。其前级还应有一状态发生器,产生64个状态和分支值。

(2)累加器、比较器和判决器。分别用来进行软距离的累加,比较各路径度量值的大小并选择输出信息元的值。

(3)路径寄存器:用来存储幸存路径。

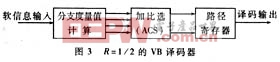

模块设计如图3示。

分支度量值计算部分,首先根据接收的软判决信息计算出每一时刻各分支度量值,在Depuncture模块输出禁止脉冲的位置不能进行度量值运算。将该结果送入加比选电路,由表1所得的各状态间转移时的输出分别累加分支度量,并利用比较和选择电路得到留选路径,把此信息送入路径寄存器。当路径寄存器中64个状态的路径度量相等时,经过大数判决电路输出译码信息,送入下级的误码监控和自同步电路。

2.2.2 Depuncture电路

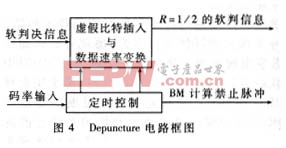

在发端经编码和删除后的数据具有大于1/2速率的数据率。为了不增加译码器的难度,采用如图4所示结构的Depuncture电路,把数据速率变回1/2,并在约定的位置插入虚假码元。通过定时控制电路来确定插入虚假比特的时刻,同时产生禁止计算脉冲,与生成的并行数据一起送入下级。

2.2.3 自同步电路

在传输数据的过程中,以2/3码率为例,它的传输序列格式为"X1Y1Y2",即删除了"X2"位置的码元。在接收到的软判决信息序列中,首先必须确定"X1"位置的数据,否则就无法确定插入虚假码元的位置。而"X1"这一起始信息系统无法传送,在本设计中自同步电路就是来完成捕获"X1"这一功能的。如图2后半部分所示,译码器先假定任一位置为"X1",通过译码结果结合误码监控来判断是否同步,并把这一信息反馈给Depuncture电路,同步标识SYN为高则表明电路同步,前级就会维持该同步;否则,前级电路将会继续捕获,直至电路同步。

评论