一种嵌入式USB2.0主机控制器IP核的研究与设计

1 引言

从通用串行总线(USB) 问世, 到协议规范2. 0版本, USB 在不断自我完善, 并走向成熟。 USB 的拓扑结构中居于核心地位的是主机(Host), 任何一次USB 的数据传输都必须由主机来发起和控制, 而目前, 大量扮演主机角色的是个人电脑( PC)。所有USB 设备都只能在PC 上使用, 只能通过PC 来进行相互的文件和数据交换。 没有了PC, 这些设备就失灵了( 指数据交换的功能)。

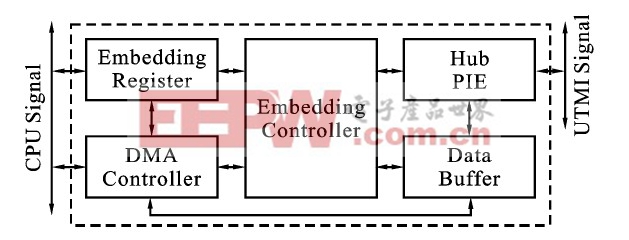

因此, 如何将USB 应用到嵌入式领域? 如何实现USB 点对点的通信?0等问题, 开始进入了USB开发者的讨论议程。 嵌入式USB 主机的设计在国内处于刚刚起步的阶段, 仅有不多的半导体公司提供接口芯片, 还很少有完整的嵌入式USB 主机产品上市。 厂家和USB 论坛所能提供的Demo 也限于依靠嵌入式操作系统WinCE 和Linux 等。因此, 项目研究具有一定的领先性。 正是在这种背景下, 业界和用户的需求呼唤USB 主机实现嵌入式化。 本设计也是基于这种背景设计了一种支持高速和全速的嵌入式USB2. 0 主机控制器IP 核, 如图1 所示。

图1 嵌入式USB2. 0 主机控制器结构

2 主机控制器IP 核的设计

2. 1 主控制器

主控制器是整个USB 主机设计中的核心模块,它控制着嵌入USB 主机控制器中其它所有模块, 此模块主要采用一个总状态机来实现其控制作用, 如图2 所示。

图2 主控制状态机

其中每个状态下又有相应的子状态机。 当EOF1( end of frame1) 到来时, 将进入等待发送SOF( start of frame) 状态, 当传输数据有效时, 会有两种传输情况, 如果是OUT 传输或( setup) 配置时, 嵌入式主机读取存储器中数据, 数据读取完后会自动跳转到PIE 模块中的OUT 传输或setup 的子状态机来完成相应的具体操作并进入传输等待状态(waitfor eot) , 等待操作完成, 相应操作完成后, PIE 模块置EOT( end of transfer) 信号为1来宣告当前传输完成, 同时会更新状态寄存器中数据准备下一次操作。 当为IN 或ping 传输时, 与OUT 或setup 传输类似, 都会跳转到相关模块来完成相应的具体操作。

评论