用OpenCV和Vivado HLS加速基于Zynq SoC的嵌入式视觉应用开发

Vivado HLS编译器流程的最后两步就是RTL实现和IP封装。这是Vivado HLS编译器中自动进行的两步,不需要用户具备RTL方面的知识。针对赛灵思产品组合中不同器件的RTL创建优化细节内置在编译器中。在此阶段,为满足需求,我们提供了经过全面测试和验证的按钮式工具,能生成基于时序和基于FPGA架构的RTL。Vivado HLS编译器的输出自动封装为IP-XACT等其它赛灵思工具能接受的格式,因此无需进行其它操作,就可在Vivado中使用HLS生成的IP核。

本文引用地址:http://www.eepw.com.cn/article/234277.htm赛灵思的OpenCV库为用Vivado HLS进行设计优化提供了捷径。这些库预先特性描述后能提供1080p分辨率的像素处理功能。引导Vivado HLS编译器进行优化的细节已嵌入在这些库中。这样,您就能快速自如地将桌面环境中的OpenCV理念应用迭代为Zynq SoC上运行的OpenCV应用,均可在ARM处理器和FPGA架构上操作。

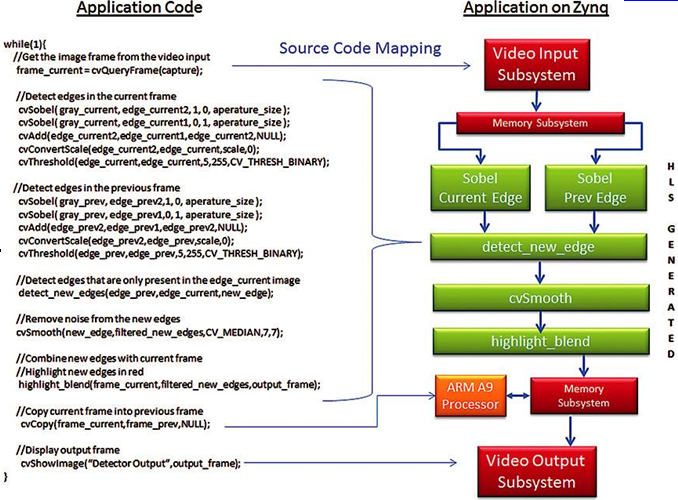

图3概述了用OpenCV进行运动检测应用开发流程。该设计的目的就是通过比较当前帧和前一帧来检测视频流中的移动物体。算法的第一阶段要检测前后两帧的边缘。数据缩减运算(data-reduction operation)便于分析连续帧之间的相对变化。边缘信息提取出来后,通过边缘对比可以检测出当前图像中出现而前一图像中不存在的边缘。检测出来的新边缘则构成运动检测掩膜图像。最新边缘检测结果在当前图像上凸显前,应考虑到图像传感器噪声的影响。各帧的噪声可能不同,会导致运动检测掩膜图像中出现随机错误边缘。因此我们必须过滤图像,减少噪声对算法质量的影响。

图5 采用可编程架构的Zynq SoC上的运动检测

在该应用中,可通过在运动检测掩膜图像上采用7x7中值滤波器来降噪。中值滤波器的主要就是取7x7相邻像素窗口的中值,然后将中值作为窗口中心像素的最终值进行报告。降噪后,运动检测掩膜图像结合于实时输入图像并用红色凸显出运动边缘。

您可全面实现应用,运行在ARM处理子系统上,采用Zynq SoC源代码映射,如图4所示。实现过程中仅有的硬件元素就是cvget-frame和showimage函数。这两个视频I/O函数用FPGA架构中的赛灵思视频I/O子系统实现的。在cvgetframe函数调用时,视频I/O子系统的输入端负责处理所有细节,从HDMI接口抓取并解码视频流,再把像素数据存入DDR存储器。Showimage函数调用时,该子系统负责将像素数据从DDR存储器传输到视频显示控制器,以驱动电视机或其它符合HDMI标准的视频显示设备。

Vivado HLS优化的、支持硬件加速的OpenCV库能将图4中的代码移植到FPGA架构中的60fps实时像素处理流水线上。OpenCV库为需要硬件加速的OpenCV元素提供基础功能。如果没有硬件加速,也就是说如果仅在ARM处理器中运行所有代码的话,那么该算法吞吐量仅为每13秒1帧(也就是0.076fps)。图5显示了Vivado HLS编译后的应用的新映射。请注意,原系统的视频I/O映射可重复使用。此前正在ARM处理器上执行的算法的计算内核,现在可编译到多个Vivado HLS生成的IP模块中。这些模块连接至Vivado IP Integrator中的视频I/O子系统,针对60fps、1080p的视频处理进行了优化。

Zynq SoC和Vivado设计套件提供的All Programmable环境非常适合以最新高分辨率视频技术所要求的高数据处理速率运行的嵌入式视觉系统的设计、原型设计和测试。采用OpenCV中的开源库集是在较短开发时间内实现高标准计算机视觉应用的最佳选择。由于OpenCV库用C++编写,因此我们用Vivado HLS创建的源代码能高效转换为Zynq SoC FPGA架构中的硬件RTL,并可用作方便易用的处理加速器,且不影响OpenCV最初设想的设计环境的灵活性。

c++相关文章:c++教程

评论