从正反馈级获得迟滞的非稳态多谐振荡器

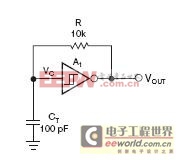

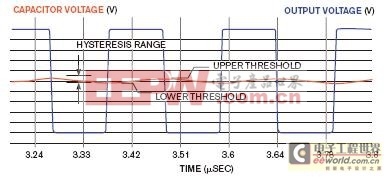

很多设计都采用基于逻辑元件的非稳态多谐振荡器,最简单的办法是围绕一个单反相施密特触发转换器的RC反馈回路(图1)。输出端将电容充电至较高的开关阈值,在该点上输出切换至其相反状态,阈值转换为一个不同值,而电容的充电电流反向。当电容的电压跨越较低阈值时,输出与阈值均转换为原来的值,过程重复。时序取决于RC时间常数与两个阈值之间宽度所决定的迟滞时间(图2)。不幸的是,虽然转换器制造商在数据表中给出了器件的迟滞电压,但范围相当大。另外,它们还与温度有一些关联。这些不确定性导致在设计电路时很难以做出一个预期的振荡频率。

图1,采用一个施密特触发器和一个RC网络的基本非稳态多谐振荡器。

图2,一只器件的迟滞主要确定了开关的阈值。

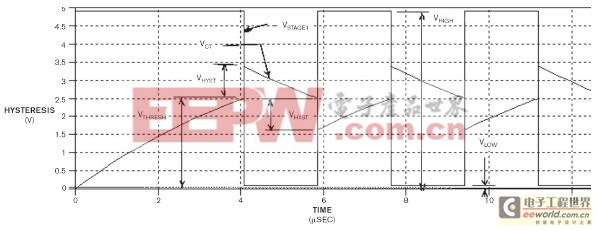

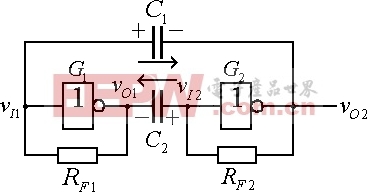

简单的转换器(没有可过冲超出标称阈值的迟滞)将电容充电至其阈值电压,并停止在其狭窄的线性区间内。在这个点上,从反相输出到输入端的负反馈将输出稳定到阈值电压。增加另一个反相级可采用正反馈方式注入一种不同形式的迟滞,正反馈由外接无源元件所确定(图3)。

正反馈级可为一个简单的反相级提供迟滞" src="http://editerupload.eepw.com.cn/fetch/20140213/231898_1_2.jpg" />

图3,增加一个正反馈级可为一个简单的反相级提供迟滞。

无论第1级何时跨越其阈值,附加的第2级会通过一个反馈电容注入额外的电荷,使时序电容的电压跳过阈值。RC充电电流转换方向,返回阈值电压。当回到阈值电压时,迟滞注入电路再次使电压跳过目标值,于是RC时序电路必须再次使充电电流反向,以搜寻阈值电压(图4)。这个过程以一种可预期的速率不断地持续。在方程中,CT为时序电容,CH为迟滞电容,VTHRESH是阈值电压,VLOW为低输出电压,VHIGH而为高输出电压。

图4,迟滞的来源是从第2级的突发充电,它以一个已知的固定量,使时序电容电压跳过开关阈值。

可以查看迟滞过冲电压VHYST,它是由时序电容CT和迟滞电容CH构成的电容分压器的结果。当第1级转换第2级时,其输出从一个低值跳到一个高值,或者从一个高值跳到一个低值,跳跃的量为VHIGH–VLOW,而时序电容的电压跳跃的幅度为VHYST=(VHIGH–VLOW)(CH/(CH+CT))。其次,时序电容通过时序电容和迟滞电容吸入电流,其电压放松至第1级的输出电压。

于是,弛豫时间常数为R(CT+CH),弛豫电压为VCT=(VTHRESH+VHYST–VLOW)exp(–t/R(CT+CH))或VCT=(VHIGH–(VTHRESH–VHYST))exp(–t/R(CT+CH)),取决于发生在哪个半周期。从VTHRESH+VHYST可以计算出VTHRESH,因t1=–R(CT+CH)ln((VTHRESH–VLOW)/(VTHRESH+VHYST–VLOW))。对另半周期,t2=–R(CT+CH)ln((VHIGH–VTHRESH)/(VHIGH–VTHRESH+VHYST))。

在总周期中,应增加通过第1级和第2级的总传播时间(tPLH+tPHL)。除非你希望电路工作在最高频率,否则这些传播时间会变得没有意义。因此,对周期的预测只取决于无源元件值,以及它们的公差、温度和老化系数。不过,CT与CH的串联组合对第2级呈现出一个容性负载。这个负载会影响第2级的上升与下降时间,必须在总周期T上增加它们的和。

当使用CMOS器件时(如仙童半导体公司的74VHC04),上升与下降时间取决于器件的输出电阻以及外接元件。如果将第2级建模为一个RC电路,可以用tRISE2=tFALL2=2.2RO(CTCH/(CT+CH))+tO估计出10%至90%指数上升与下降时间,其中tRISE2为上升时间,tFALL2为下降时间,RO为器件的输出电阻(74VHC04为30Ω),而tO为无负载上升时间(此种情况下,VHC04为4.5ns)。于是,总周期为:t1+t2+2(tPLH+tPHL)+tRISE2+tFALL2。

另外要注意的是,时序依赖于反相器的输出电压,以及该区间内阈值电压的位置。例如,一款输出电压接近电压轨的CMOS器件要比一个TTL(晶体管-晶体管逻辑)器件更可预测,一只有中点阈值电压的74HC器件要比一只阈值电压偏离TTL接口的HCT器件的输出更均衡。

对于较高频率,必须采用较小的电阻值、较小的时序电容值,或两者都是较小值。对于可预知的结果,时序电容值应比反相器输入电容小10倍,对一只典型CMOS器件,输入电容值在3pF至10pF范围内,R不应小到会明显拉低输出。作为一种预防性措施,迟滞电容值应不超过时序电容值,因此就不会超过第1级的最大输入电压。如果迟滞电容值要比时序电容大得多,则阈值电压与迟滞电压会分别达到7.5V和-2.5V。74VHC04器件用5%电阻和20%电容验证了该计算。

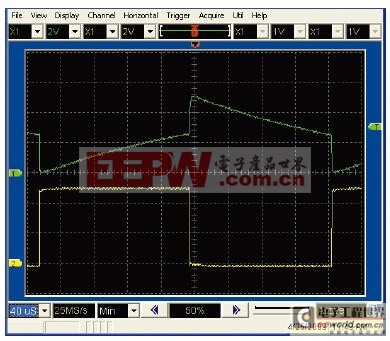

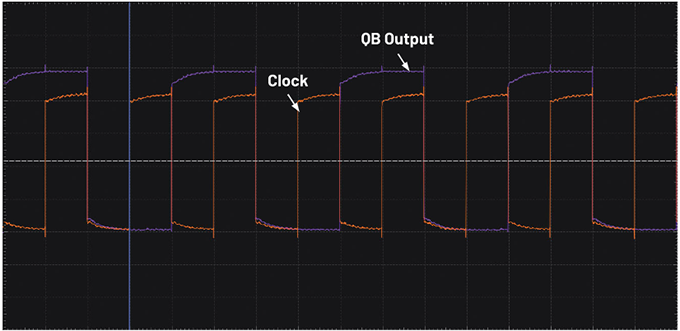

图5,电路在低频性能良好。

表1汇总了各个结果, 它们处于元件公差范围内。图5给出了一个典型的输入与输出图。

评论