浅谈PCB的阻抗控制

多层板的结构:

为了很好地对PCB进行阻抗控制,首先要了解PCB的结构:

通常我们所说的多层板是由芯板和半固化片互相层叠压合而成的,芯板是一种硬质的、有特定厚度的、两面包铜的板材,是构成印制板的基础材料。而半固化片构成所谓的浸润层,起到粘合芯板的作用,虽然也有一定的初始厚度,但是在压制过程中其厚度会发生一些变化。

通常多层板最外面的两个介质层都是浸润层,在这两层的外面使用单独的铜箔层作为外层铜箔。外层铜箔和内层铜箔的原始厚度规格,一般有0.5OZ、1OZ、2OZ(1OZ约为35um或1.4mil)三种,但经过一系列表面处理后,外层铜箔的最终厚度一般会增加将近1OZ左右。内层铜箔即为芯板两面的包铜,其最终厚度与原始厚度相差很小,但由于蚀刻的原因,一般会减少几个um。

多层板的最外层是阻焊层,就是我们常说的“绿油”,当然它也可以是黄色或者其它颜色。阻焊层的厚度一般不太容易准确确定,在表面无铜箔的区域比有铜箔的区域要稍厚一些,但因为缺少了铜箔的厚度,所以铜箔还是显得更突出,当我们用手指触摸印制板表面时就能感觉到。

当制作某一特定厚度的印制板时,一方面要求合理地选择各种材料的参数,另一方面,半固化片最终成型厚度也会比初始厚度小一些。下面是一个典型的6层板叠层结构:

PCB的参数:

不同的印制板厂,PCB的参数会有细微的差异,通过与上海嘉捷通电路板厂技术支持的沟通,得到该厂的一些参数数据:

表层铜箔:

可以使用的表层铜箔材料厚度有三种:12um、18um和35um。加工完成后的最终厚度大约是44um、50um和67um。

芯板:我们常用的板材是S1141A,标准的FR-4,两面包铜,可选用的规格可与厂家联系确定。

半固化片:

规格(原始厚度)有7628(0.185mm),2116(0.105mm),1080(0.075mm),3313(0.095mm ),实际压制完成后的厚度通常会比原始值小10-15um左右。同一个浸润层最多可以使用3个半固化片,而且3个半固化片的厚度不能都相同,最少可以只用一个半固化片,但有的厂家要求必须至少使用两个。如果半固化片的厚度不够,可以把芯板两面的铜箔蚀刻掉,再在两面用半固化片粘连,这样可以实现较厚的浸润层。

阻焊层:

铜箔上面的阻焊层厚度C2≈8-10um,表面无铜箔区域的阻焊层厚度C1根据表面铜厚的不同而不同,当表面铜厚为45um时C1≈13-15um,当表面铜厚为70um时C1≈17-18um。

导线横截面:

以前我一直以为导线的横截面是一个矩形,但实际上却是一个梯形。以TOP层为例,当铜箔厚度为1OZ时,梯形的上底边比下底边短1MIL。比如线宽5MIL,那么其上底边约4MIL,下底边5MIL。上下底边的差异和铜厚有关,下表是不同情况下梯形上下底的关系。

介电常数:半固化片的介电常数与厚度有关,下表为不同型号的半固化片厚度和介电常数参数:

板材的介电常数与其所用的树脂材料有关,FR4板材其介电常数为4.2—4.7,并且随着频率的增加会减小。

介质损耗因数:电介质材料在交变电场作用下,由于发热而消耗的能量称之谓介质损耗,通常以介质损耗因数tanδ表示。S1141A的典型值为0.015。

能确保加工的最小线宽和线距:4mil/4mil。

当我们了解了多层板的结构并掌握了所需要的参数后,就可以通过EDA软件来计算阻抗。可以使用Allegro来计算,但这里我向大家推荐另一个工具Polar SI9000,这是一个很好的计算特征阻抗的工具,现在很多印制板厂都在用这个软件。

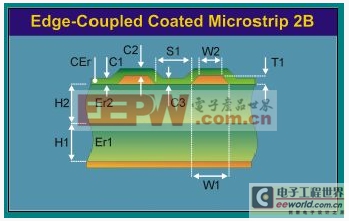

无论是差分线还是单端线,当计算内层信号的特征阻抗时,你会发现Polar SI9000的计算结果与Allegro仅存在着微小的差距,这跟一些细节上的处理有关,比如说导线横截面的形状。但如果是计算表层信号的特征阻抗,我建议你选择Coated模型,而不是Surface模型,因为这类模型考虑了阻焊层的存在,所以结果会更准确。下图是用Polar SI9000计算在考虑阻焊层的情况下表层差分线阻抗的部分截图:

由于阻焊层的厚度不易控制,所以也可以根据板厂的建议,使用一个近似的办法:在Surface模型计算的结果上减去一个特定的值,我建议差分阻抗减去8欧姆,单端阻抗减去2欧姆。

评论