如何更好地挑战电源0.1W待机功耗需求

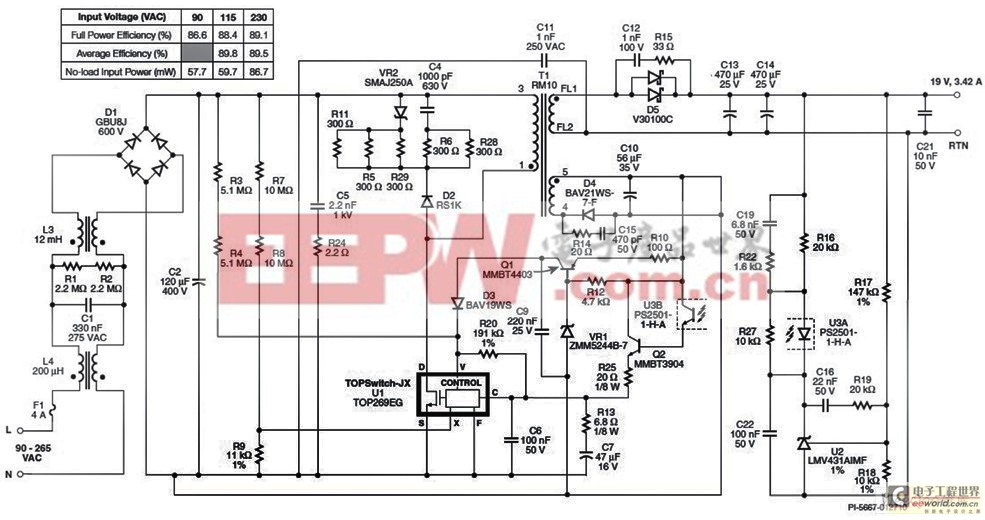

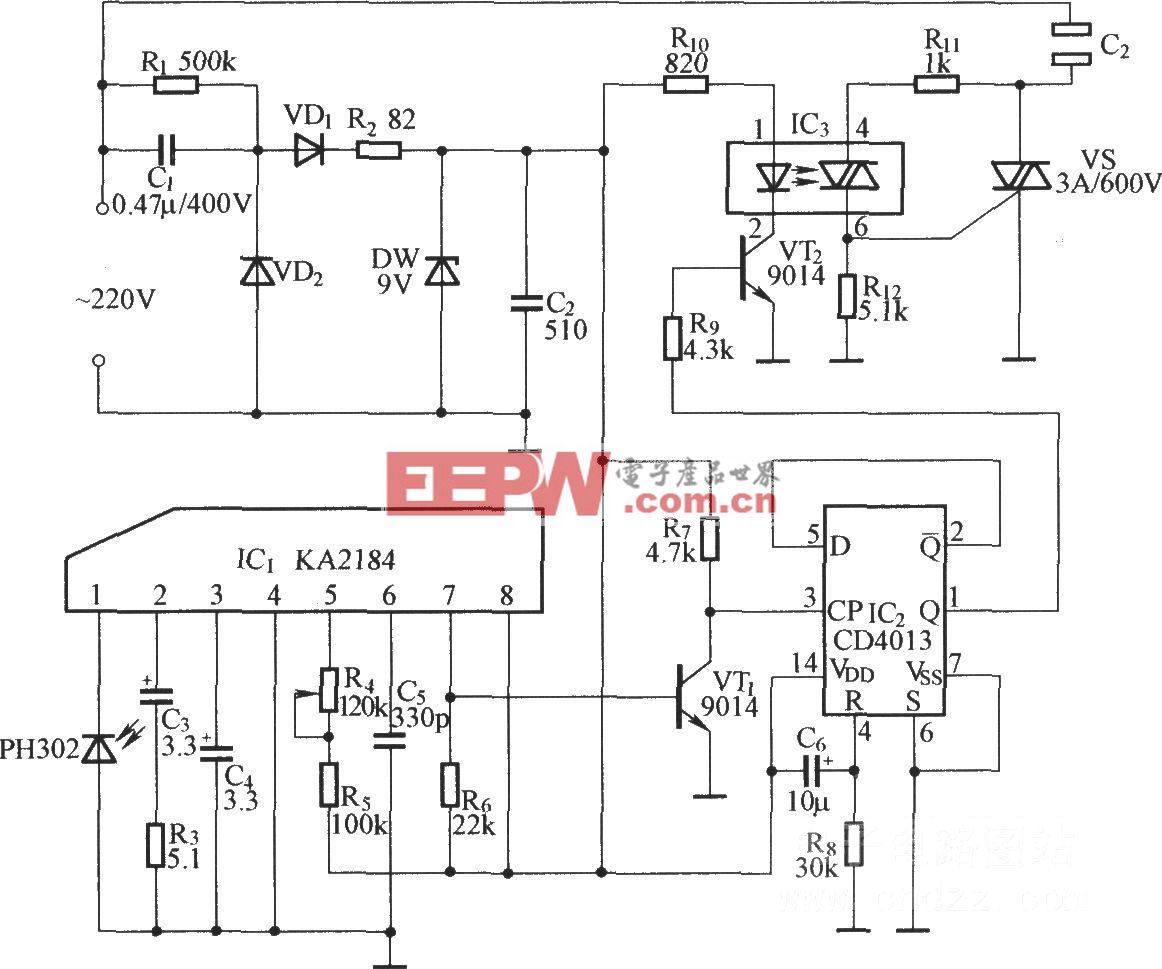

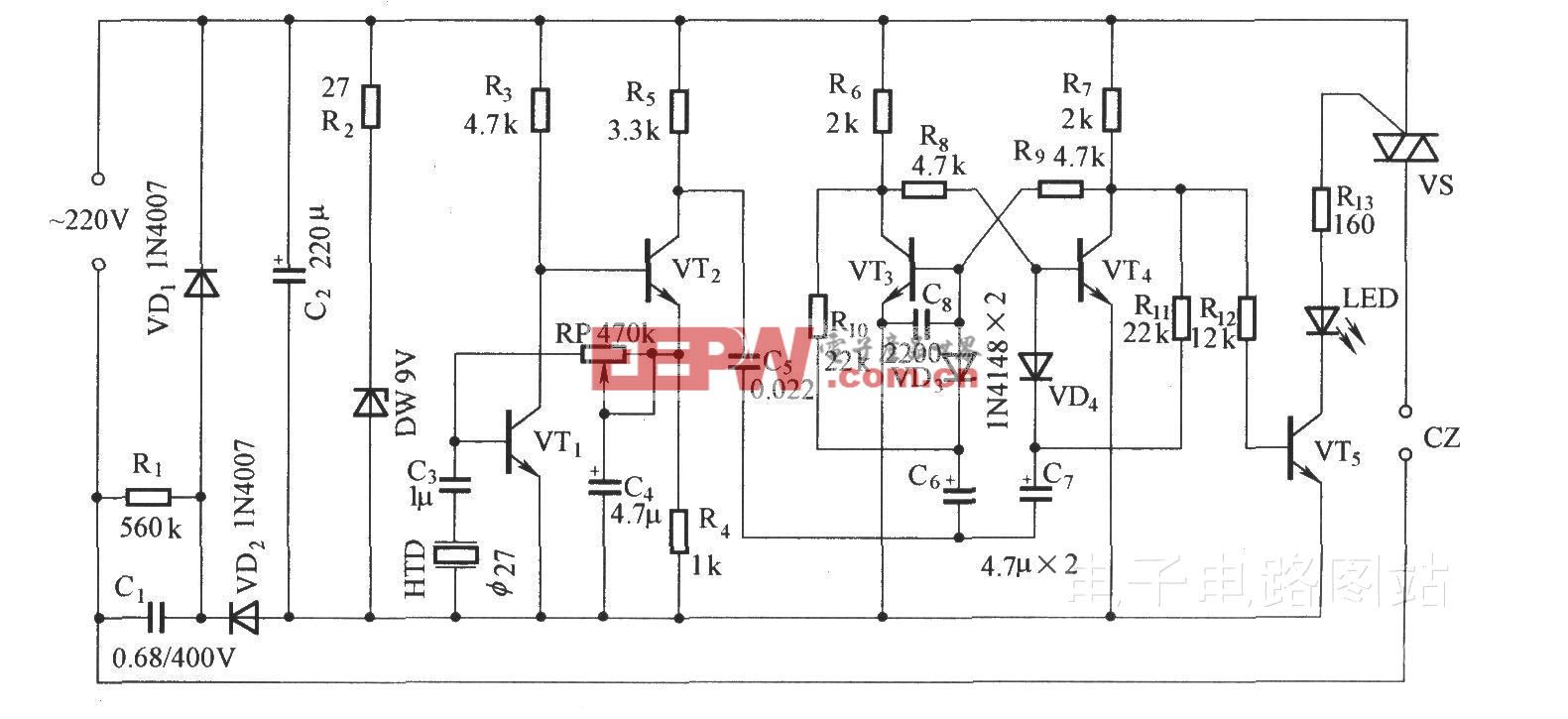

图1 电源的标准线路图

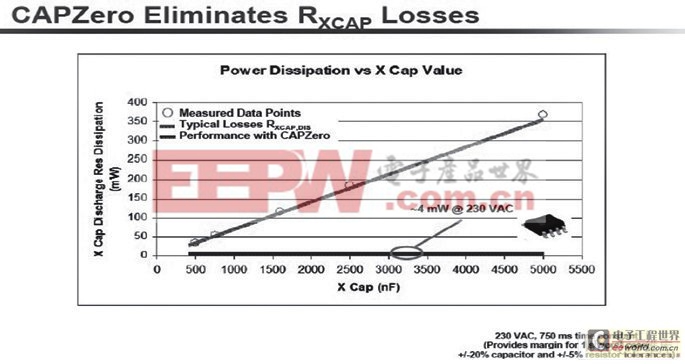

如图1虚线所圈部分,这是一个电源的EMI滤波电路,在这个电路中,请注意一下X电容C1上面并联的两个电阻,这两个电阻是起什么作用呢?电容是可以存储电能的产品,当我们电源接通交流电后,交流电会对C1充电,被充电后的电容存储着电量,当我们把电源插头从交流电源上拔出后,这个电量仍然存在于电容中,这个电容的两端直接与电源插头的两个脚相连,换言之,如果这里人体不慎碰到插头的两个脚,就会被电容上的电量触电,所以安规中强制规定,这个电容上的电量必须在电源插座被拔除后一定的时间泄放完,所以这两个电阻在这里起放电作用,是万万不能省的,但是这两个电阻直接与交流电源相连,也就是说,在电源进入待机状态后时,这两个电阻在消耗着能量,它上面的损耗有多大呢?图2中列出了跟不同X 电容匹配的电阻所生的损耗,X电容越大,放电电阻越小,其损耗就越大,结果显示,这个放电电阻上面有几十mW到几百mW的损耗,再加上其它元器件上的损耗,整机小于0.1W的目标沦为了天方夜谈。

图2

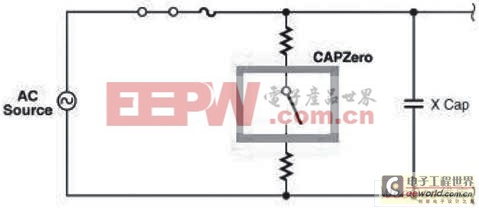

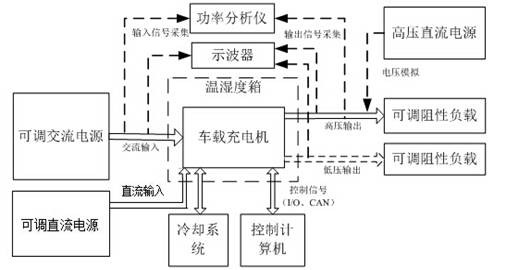

如果说在这两个电阻上串一个智能开关,如图3 所示,切断交流电源时开关吸合,从而把两个电阻连起来,快速泄放走X电容的电荷,而接上交流电源时开关切断,从而把两个电阻断开,让这时两个电阻上没有电流流过,实现零损耗,不是一个两全齐美的好方法吗?

图3

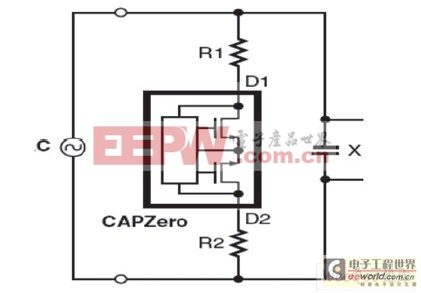

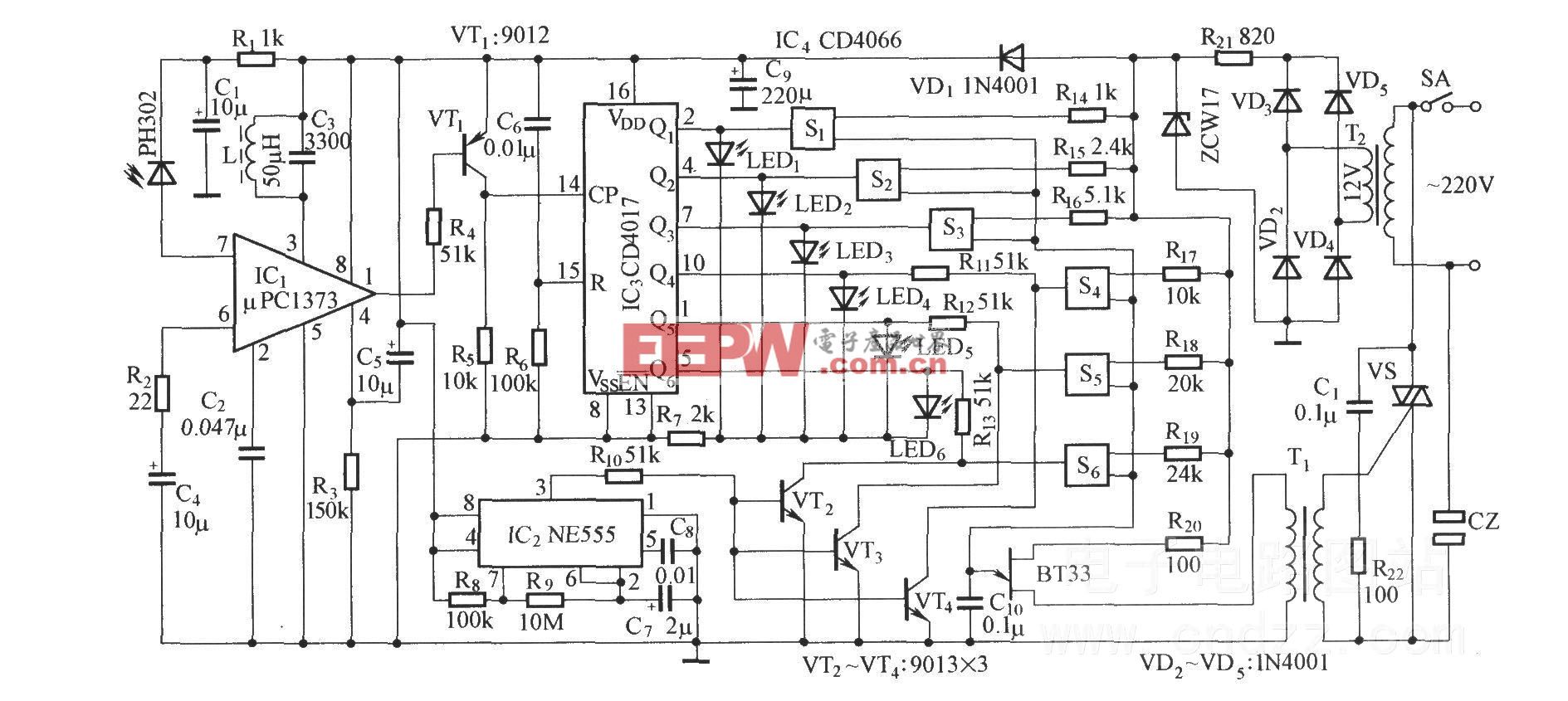

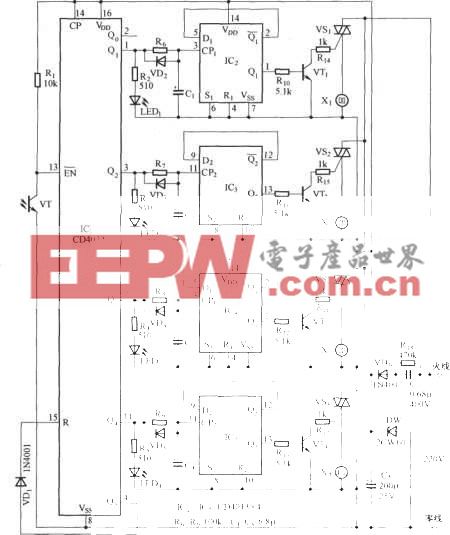

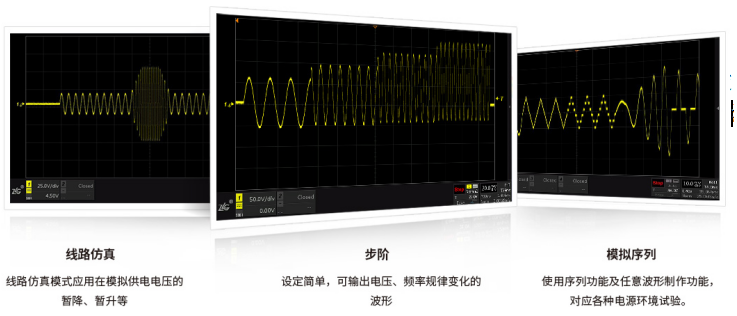

电源半导体先驱,打造绿色环保IC的创导者和领导者,美国PI公司把这一个电源工程师的想法变成了一个产品,被命名为Cap Zero,图3为其等效电路图,图4为其内部电路图,图5为其实物图,从图4中可以看出,它由检测控制电路和开关电路组成,检测控制电实时检测着X电容两端的交流电压(即电源插座上的交流电压),当X电容两端电压存在时,检测控制电路会保持相应的信号让开关电路保持关闭状态,反之,则开通。因为设计者不再担心X电容放电电阻的损耗,所以设计者可以选用更大的X 电容,减小差模电感,这让设计者在设计EMI 电路时有更多的组合方案和改进空间。

图4 内部电路图

图5

目前这一产品为SO-8的封装,电源设计者无须做任何调试,只需要在PCB板上LAYOUT上这个封装,需要时装上去,不需要时用Jump短路即可,简单易操作,可靠实用。Cap Zero的出现,在电源设计者挑战电源0.1W待机功耗的征程中,无疑又留下了光辉的一笔。

评论