时域反射仪的硬件设计与实现----关键电路设计(一)

3.1低压窄脉冲源设计

脉冲信号源的整体设计包括脉冲信号的产生模块设计、脉冲信号等效延时模块设计,脉冲信号放大、发送模块的设计。

3.1.1脉冲信号产生

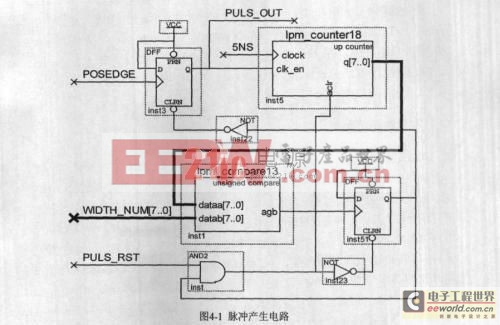

脉冲的宽度通过计数器的方式来进行控制,一个上升沿启动一个D触发器产生一个从低到高的电平变化,该电平变化作为脉冲的上升沿,同时用该高电平启动一个计数器计数,计数时钟的周期为Δt。计数值输出端作为一个比较器的一个输入,比较器的另一个输入端被预置一个计数次数N,N的大小决定脉冲宽度,当计数器的输出与N值相同时,比较器输出一个状态信号将D触发器清零,此时一个脉宽为N*Δt的脉冲信号已经产生。如图4一1所示。

从脉冲产生电路可知,POSEDGE信号通过D触发器产生脉冲信号的前沿,同时该前沿使能一个8位宽度的二进制计数器,计数器的输出与预设宽度数值做比 较,当达到预设宽度时,比较器输出端产生的上升沿信号触发另一个D触发器产生一个高电平信号(脉冲状态信号),该高电平信号将前面的D触发器清零,即输出 了脉冲信号的下降沿。PULs一ST是一个复位信号,高电平有效,即在产生脉冲以后需要将计数器和状态信号清掉,以便为下次脉冲产生做准备。可以看到,复位信号必须要和第2个D触发器的输出端进行相与后才能工作,也就是说复位信号必须在脉冲完成之后才有效。

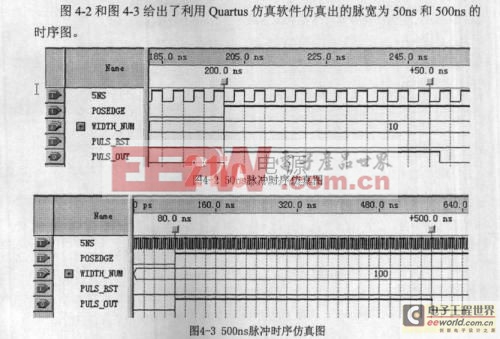

从上面两个仿真图可以观察出,产生出来的脉冲宽度都超过了设定值,产生了误差,可以看到误差,主要是因为在POSEDGE信号上升沿时,计数脉冲信号过了半个周期才到,因此该误差刚好为半个周期计数脉冲的时间,即为2.5ns,该误差就是我们常说的±1误差。在实际测量中,脉冲信号的前沿是最关心的部分,因此宽度的不准确性对于测量不会造成影响。

3.1.2脉冲信号延时

前面已经讨论过,在时基为100ns/div时,刚好达到ADC的最大采样极限(250MsPs),当时基进入更快档位时,如果要进行正常的显示就需要更多的数据。通过两种办法可以实现:软件插值和等效采样。采用软件插值的方式会导致脉冲信号沿失真,影响测量准确度,在这里采用顺序时间等效采样,即将采样信号与脉冲信号做相对延时,相对延时的时间△t越小,等效采样率越大,经过多次采样后,得到显示所需要的数据。为了保证波形刷新率,等效采样率随时基可变,即时基不同时,相对延时的时间△t也不同。与此同时,在进行顺序等效的时候,时基越小,需要的等效延时的次数越多,即显示单次波形需要采样的次数越多。

表4一1给出了在不同时基情况下的相对延时的时间△t、采样次数和等效采样率。

评论