卷积码+QPSK的中频调制解调系统的FPGA

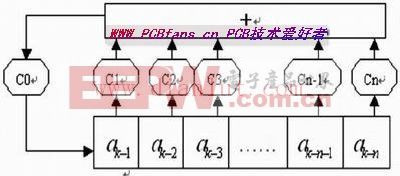

TB模块从SPM中读取当前时刻64条路径的幸存信息,根据末端状态可以找到相应的最大似然路径在时刻t的幸存信息,从而找到t-1时刻最大似然路径上的状态。依此类推,直至找到最大似然路径在t-L+1时刻的状态,状态的最高位即为译码输出。

FPGA可以实现流水线操作,而各个模块可以同时进行工作,所以需要控制模块处理各个模块间的时序关系。每个子模块都有一个控制信号,使得输入数据可以在各个模块之间进行流水操作。

由于本方案是基于各个功能单元自上至下设计的,灵活性较大,稍加修改子模块,便可以用于实现各种卷积码的Viterbi译码器。

2.2 QPSK调制与解调的FPGA实现

QPSK调制模块由成形滤波和上变频两部分组成。成形滤波具有两个功能,即限带和抗码间干扰。成形滤波采用查表的方式实现,四倍内插,升余弦滚降。形成后的数据与NCO产生的本地载波进行上变频运算。

QPSK解调的结构框图如图4所示。解调模块由下变频、低通滤波、根升余弦滤波和载波同步几部分组成。I、Q两路的调制信号先经过本地载波NCO下变频,再通过低通滤波器LPF得到基带信号。基带信号需要进行相应的根升余弦滤波。由于本地载波与发端载频之间有一定的偏差,所以要根据解调后的信号估计频差并修改要地载波NCO的参数,实现载波同步。数据经过根升余弦滤波后进行差分解码,解调后头这入译码器单元。

综上所述,系统主要功能都是在FPGA内完成的。本文选择Xilinx公司的100万门FPGA芯片XC2V1000,在ISE 6.2i环境下进行编程开发。系统的资源占用情况如表1所示。

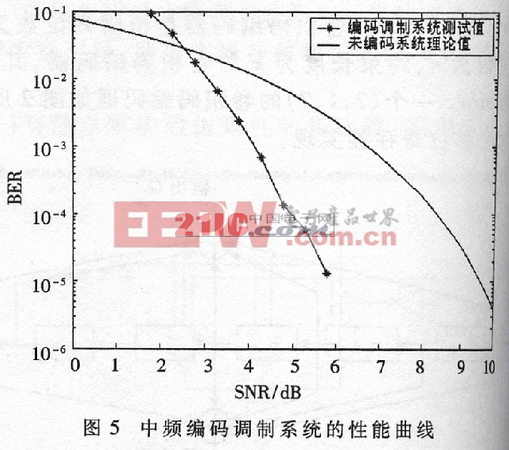

为了测试系统在噪声下的误码率性能,在发端和收端之间引入噪声源,在70MHz中频上进行数据传输。使用误码率分析仪进行现场测试,获得的测试误码率曲线如图5所示。为了方便比较,图中给出了未编码传输系统的理想误码率曲线。由于定点实现、定时同步、载波同步等误差因素,调制解调的实现损耗将近1dB;而viterbi译码的量化输入和截短译码(本方案采用3比特量化和64步截短译码)带来的实现损失约为1dB。(2,1,7)卷积码的编码增益约为5~6dB,所以测试误码率曲线与未编码传输系统的理想误码率曲线之间的差距是3~4dB。换言之,本系统的实现增益为3~4dB。

综上所述,本系统设计简单、功耗低、性能良好,可在中频范围内进行高速数据的可靠传输。在不改变系统结构的情况下,稍加修改可广泛应用于其它类型的编码调制系统中。

评论