卷积码+QPSK的中频调制解调系统的FPGA

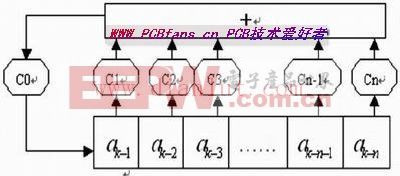

加比选单元ACS(Add-Compare-Select)模块包括若干个单个状态加比选模块ACSU,一个ACSU模块执行一个状态 的路径度量升级。ACSU模块的具体个数根据译码器的速率要求而定。对于低速的译码器,为了节约芯片的面积,可以使用较少的ACSU模块进行时分复用;而在高速Viterbi译码器的设计中,则采用全并行的结构,ACSU模块的个数等于网格图上的状态数N=2k-1。译码器开始工作时,给路径度量设定一个初始化正值。在度量升级过程中,路径度量的不断累加会造成溢出。因为在度量升级时只是比较大小,所以在每次度量升级之后,所有的路径度量值减去路径度量值中的最小值,而不会影响路径度量向的大小关系。同时,为了下次路径度量升级不出现负值,需要对所有的度量值加上一个恒定常数。经过归一化处理后的路径度量,其最大值与最小值相差不超过2 q(k-1)。

所以,对于q比特而软判决编码长度为k的Viterbi译码器,其路径度量长度为q+log2(k-1)比特。

MLD(Most-Likelihood-Decision)模块用于在所有状态的路径度量中找出最大值,具有最大路径度量的幸存路径便是最大似然路径。在时刻L时,MLD电路判决最大似然路径,将其末端节点状态送至TB模块。同时为了保证下次的路径度量升级不出现负值,还要找出最小值送到PMMI模块,在其中进行归一化处理。

PMMI模块和SPMI模块分别是ACS模块与路径度量存储器PMM(Path Metric Memory)之间和幸存路存储器SPM(Survivor Path Memory)与MLD模块之间的接口模块。同时,TB(TraceBack)模块也通过SPMI模块读取幸存路径存储器信息。针对不同的存储方式,SPMI和PMMI的复杂程度也不同。ACSU模块的复用程度越高,其接口电路越复杂。

相关推荐

-

-

-

-

-

-

-

-

-

-

-

-

sandman555 | 2005-02-05

-

-

herbertwj | 2004-08-15

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

-

-

-

xiaohua | 2002-09-24

评论