Virtex-5 LXl10的ASlC原型开发平台设计

1.4 散热管理

FPGA支持的速率越高,本身的资源密度越大,因此要关注应用中的散热管理问题。对FPGA的功率消耗进行估计,以决定是否需要散热系统。

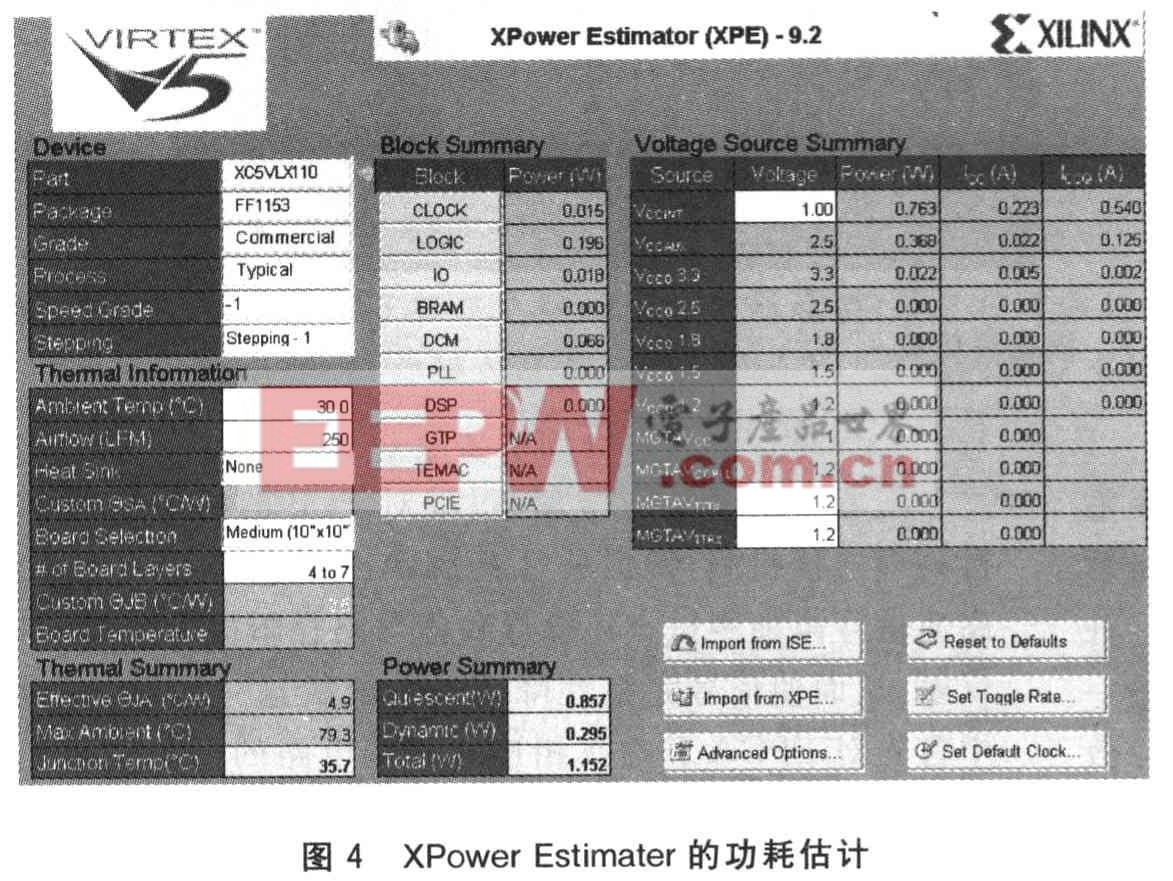

XPower Estimater是一款基于Excel的软件,通过对设计资源的利用,包括逻辑资源、DCM、PLL、I/0类型、触发率(toggling rate),以及其他与FPGA设计密切相关的信息,对FPGA的功耗进行估算。图4为利用XPE进行设计功耗估算的截图。

1.5 信号完整性分析

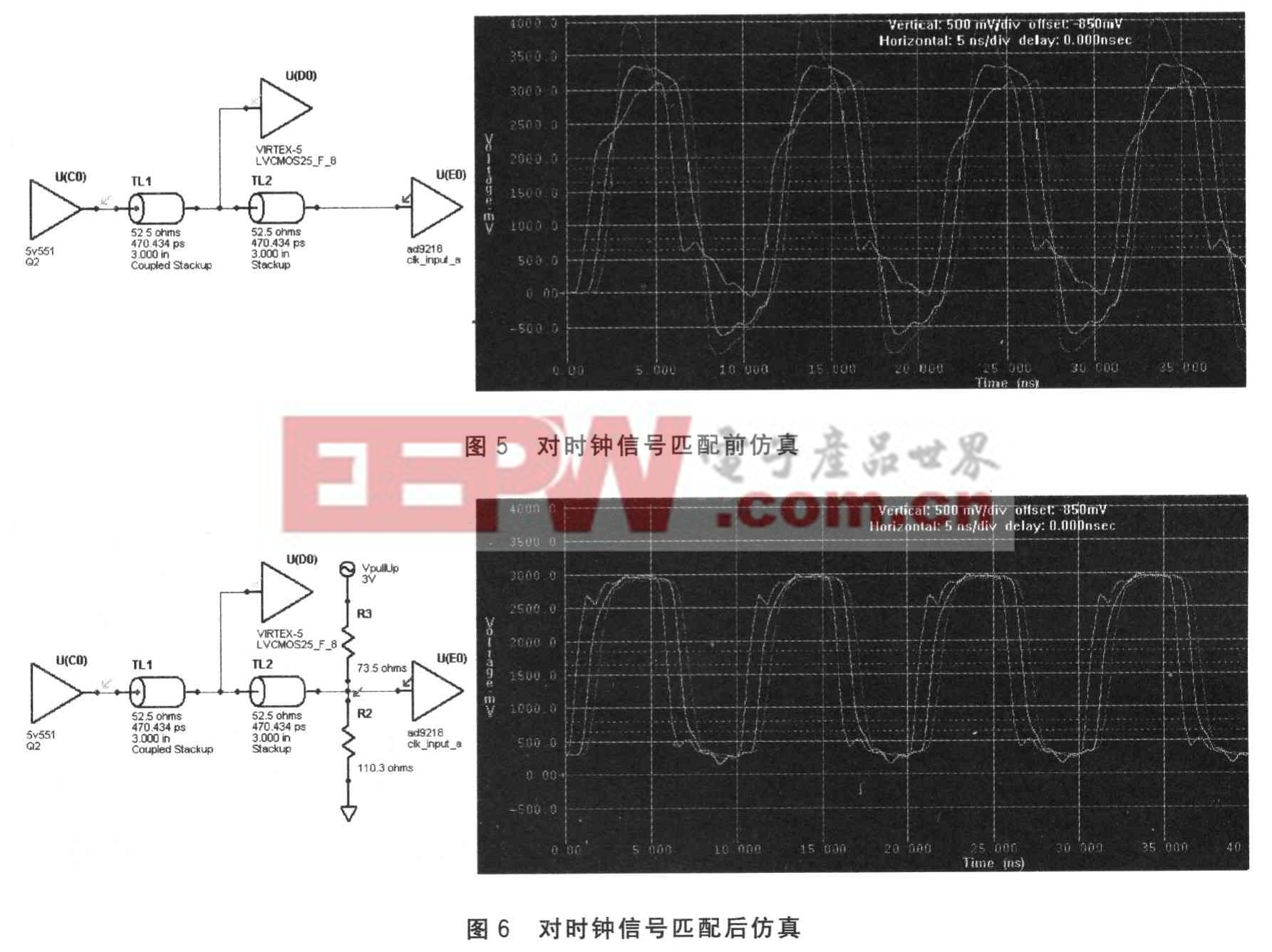

在时域和频域对设计的连接拓扑结构(PCB叠层、驱动端、接收端、连接器、通孔等等)进行信号完整性分析,目的是要评估和减小信号从驱动端到接收端的反射、串扰以及EMI/EMC等问题。通过仿真分析得到的约束形式能有效指导PCB布局布线工具进行layout设计。进行信号完整性分析,首先要确定与FPGA相接的外围器件的I/O特性及其约束,进而对FPGA采用何种I/0类型以及端接匹配机制有一个大致的了解,然后是通过仿真对采用的I/O类型及端接电路的各个参数进行定义及优化。

(1)前仿真

S1分析一般主要从高速信号、对时序要求较高的信号、走线最长的信号、负载最多的信号开始,因为这些信号线通常最容易引起SI问题。确定关键信号在仿真环境中建立起相应的拓扑模型。

通过仿真能定义出最长连接走线以及其他满足噪声裕量(匹配电路、端接方式等)的网络属性。确定FPGA驱动缓冲特性,例如I/O标准、驱动能力以及回转率,使信号完整性问题、EMI/EMC问题最小化,同样也对接收端I/0属性进行定义。进行串扰仿真以保证相邻走线不会引起串扰问题。定义端节匹配方式。

图5、6是对时钟网络匹配前和匹配后进行的仿真图形对比。

评论