Virtex-5 LXl10的ASlC原型开发平台设计

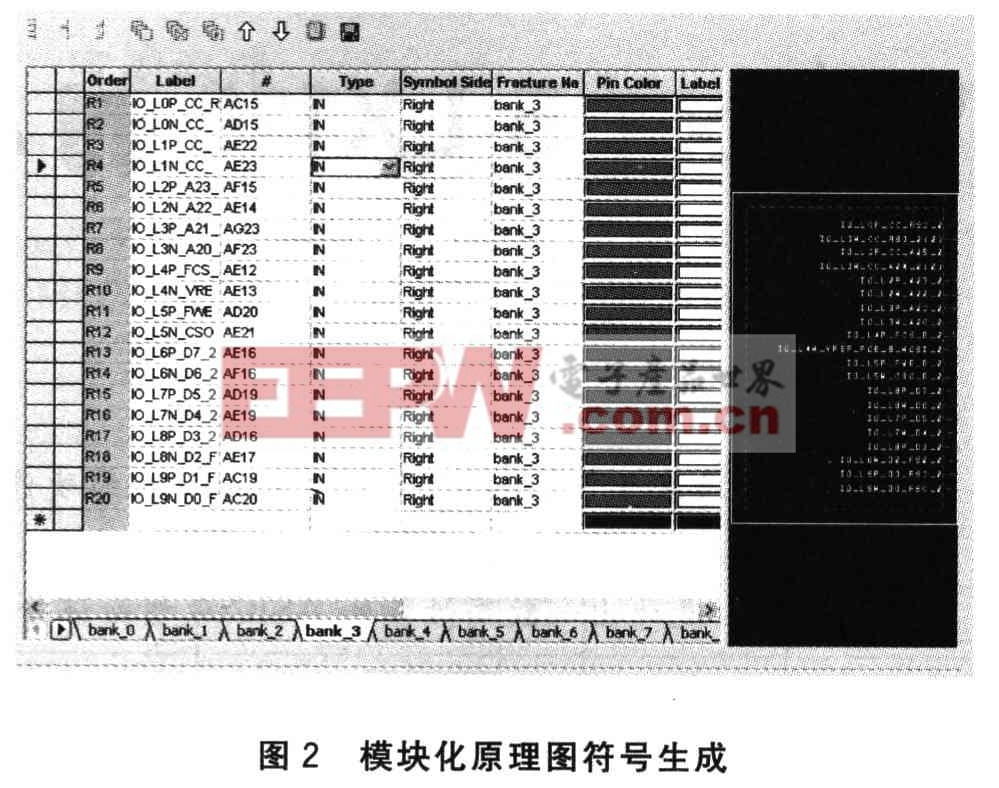

接下来为FPGA创建结构化的原理图符号。由于FPGA本身I/0的复杂性和可配置性,将整个FPGA分割为多个子模块能够有效地减轻设计的复杂度,也便于管理和检查。图2显示了利用Mentor Dxdesigner’原理图符号生成向导生成模块化原理图符号的设计过程。原理图符号生成之后就可以在原理图设计环境进行原理图的设计,指定各个模块的连接关系。

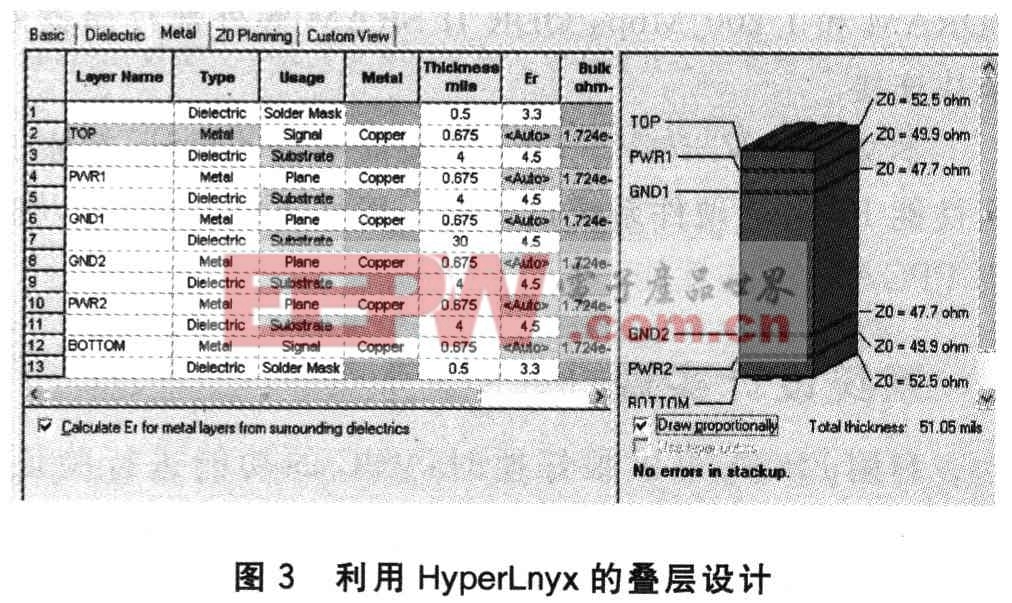

1.3 PCB叠层定义

对。PCB叠层、材料和尺寸的设计需要考虑以下因素:

◆走线层的数量需要考虑到封装特性、设计所用的I/()数目以及间距;

◆芯片互联线的数据传输速率,信号的上升、下降时间对PCB材料、尺寸以及走线方式和制板工艺的限制;

◆元件所需的不同供电和参考电压,对电源层的规划和设计;

◆成本问题(利用盲孔、盲埋孔、微通孔等工艺能有效地减少叠层数目,以达到降低成本的目的)。

该设计中,与FPGA互联的信号线约为130条,包括配置电路信号线、时钟信号线及其他I/O信号。选用上下两个走线层。考虑到多个电源供电,设置2个电源平面、2个地平面。整个PCB采用6层板结构设计,信号层目标阻抗50 Q。

利用HyperLnyx叠层设计如图3所示。

评论