一种基于FPGA的新型数字电压表研究与设计

4.2 信号采样周期自调整算法

为协调好数据精度和系统负担两者之间的关系,对于叠加周期信号的输入信号Vi,规定单个周期的数据采集不少于8个点,因此要对AD0809的采样周期进行自适应调整。这里使用过零点检测的方法,如果叠加信号的周期在0~25 Hz范围内,采样周期为5 ms。叠加信号周期在25~50 Hz时,采样周期为2 ms;叠加信号周期在50~100 Hz时,采样周期为1 ms。

设采样周期的初始值为2 ms,采样数为100点。则有:首先采集100个数据,计算平均值,作为输入信号Vi的均估值(平均值的估计值);再采集100个数据,与Vi的均估值进行比较,计算过零点的数量并统计;根据此数量,调整采样周期,当此数量大于20时,令采样周期为1 ms。当此数量不大于10时,令采样周期为5 ms。其他令采样周期为2 ms。

4.3 检测叠加信号周期算法

依旧采用检测过零点的数目来检测周期。

设采集的数据点为1O0个,计算均值,作为输入信号Vi的均估值;再采集数据,与Vi的均估值进行比较,计算过零点的数量并统计,同时统计每个数据过零点的时刻;检测到三个过零点时,判断其是否符合均匀分布,判断是否检测到一个周期。若检测到一个周期,则停止检测并计算此周期,否则继续检测。若检测到相当数量的数据点,过零点数量仍小于3个,则认为输入信号为直流信号。

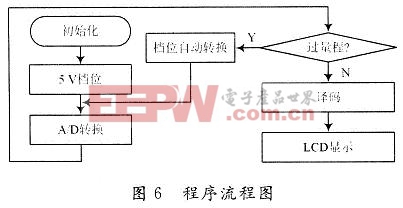

5 程序流程

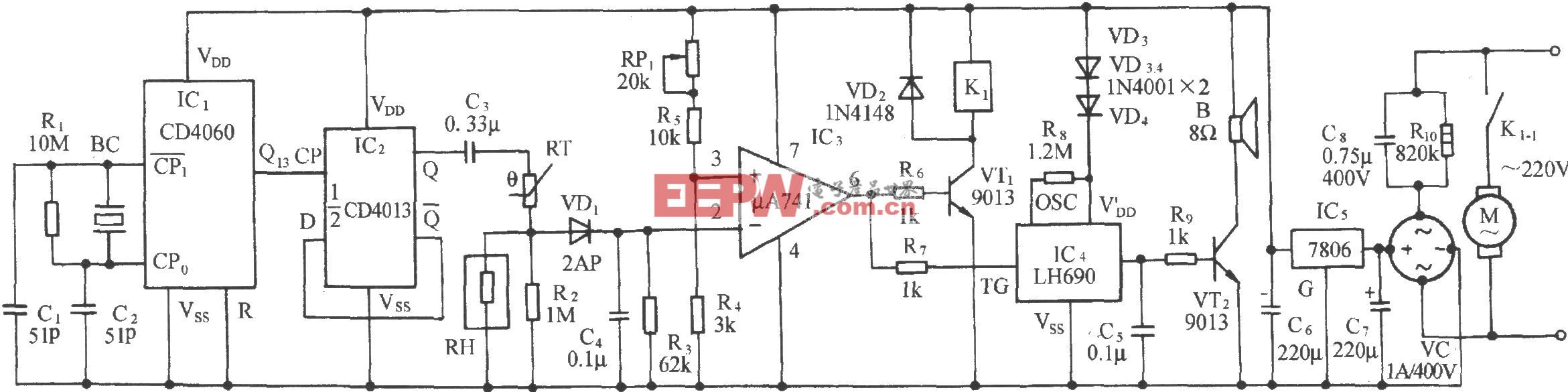

程序流程如图6所示。

6 测试结果分析

采用高精度数字多用表UT88B输出值作为标准值。由表1所示。

由数据对比可以看出,在O~5 V档位上,该数字电压表的误差基本在O.01 V内。在O~50 V档位上,误差有所增大,但也控制在O.02 V以内,体现了ADC0809的转换精度,电路整体设计合理可靠。至于O.02 V以内的偏差,可修改程序,采用软件的方法进行数据校正,也可以进一步校正A/D的基准电压。

7 结语

利用现场可编程门阵列技术,设计了该新型数字式电压表。用软件替代诸多硬件,在一块高性能FPGA芯片上,实现采样时序的控制、档位的判断选择、码制的转换和LCD驱动,极大地提高了系统集成度和可靠性。文中重点介绍了档位电路和FPGA内部模块的设计以及关键算法的实现步骤。由测试结果,可看出该仪表测量范围较宽,测量精度较高,能够满足物理实验中电量的测量要求。经实际使用证明,系统运行稳定、操作方便。为了方便电压表系统与计算机直接通信,还可进一步增加RS 232接口,进行电平转换,可将测得的数据实时导入计算机中使用。

评论