这里采用的ADC0809是单片双列直插式集成芯片,是8通道8位A/D转换器,其主要特点是:分辨率为8位;总的不可调误差±1 LSB;当模拟输入电压范围为0~5 V时,可使用单一的+5V电源;转换时间为100μs;温度范围-40~+85℃;不需另加接口逻辑可直接与CPU连接;可以输入8路模拟信号;输出带锁存器;逻辑电平与TTL兼容。

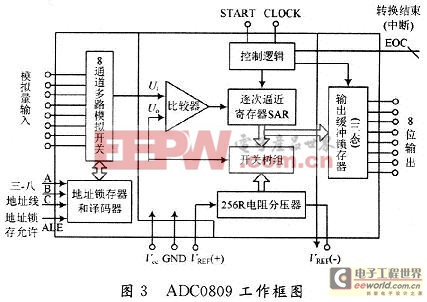

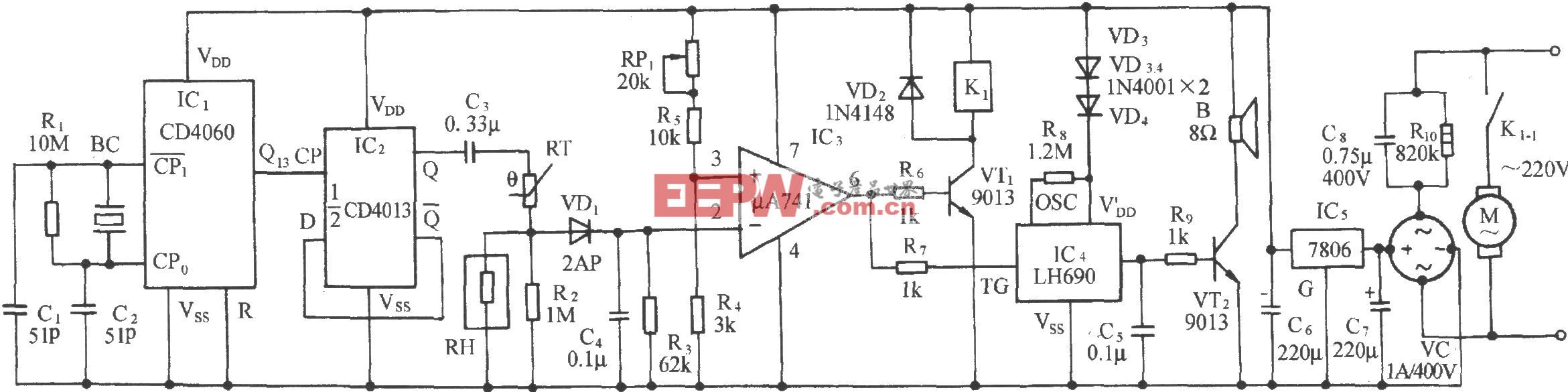

ADC0809带有8位转换器、8位多路切换开关以及与微处理机兼容的控制逻辑的CMOS组件。它的8位A/D转换器转换方法为逐次逼近法。在A/D转换器的内部,含有一个高阻抗斩波稳定比较器,一个带有模拟开关树组的256R分压器,以及一个逐次逼近的寄存器。8路的模拟开关由地址锁存器和译码器控制,可以在8个通道中任意访问一个单边的模拟信号。其工作框图如图3所示。

该A/D转换器无需调零和满量程调整。由于多路开关的地址输入能够进行锁存和译码,而且三态TTL输出也可以锁存,易于与微处理器进行接口。

如图3所示,它由两大部分所组成:第一部分是8通道多路模拟开关,它用于控制C,B,A端子和地址锁存允许端子,可使其中一个通道被选中;第二部分为一个逐次逼近型A/D转换器,它由比较器、控制逻辑、输出缓冲锁存器、逐次逼近寄存器以及开关树组和256R电阻分压器组成。后两种电路,即开关树和256R电阻分压器,组成了D/A转换器。控制逻辑用来控制逐次逼近寄存器从高位到低位逐次取1,然后将此数字量送到开关树组,即8位开关,用来控制开关S7~S0与参考电平相连接。参考电平经256R电阻分压器,输出一个模拟电压Uo,Uo,Ui在比较器中进行比较。当Uo>Ui时,本位D=O;当Uo≤Ui时,则本位D=1。因此,从D7~D0比较8次即可逐次逼近寄存器中的数字量,即与模拟量Ui所相当于的数字量相等。此数字量送入输出锁存器,并同时发转换结束脉冲。

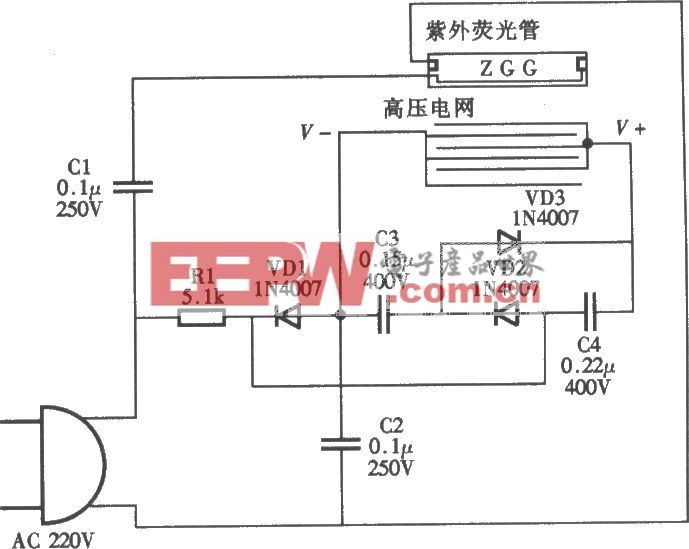

该电压表电路中,ADC0809的工作时序如图4所示。主要控制信号:START是转换启动信号,高电平有效;ALE是3位通道选择地址(ADDC,ADDB,ADDA)信号的锁存信号。当模拟量送至某一输入端,由3位地址信号进行选择,而地址信号由ALE锁存;EOC是档位转换的状态信号。EOC输出高电平时,表示转换结束;在EOC的上升沿后,若使能输出信号OE为高电平,则三态缓冲器打开,将转换完毕的8位数据结果输至数据总线,至此ADC0809的一次转换结束。

评论