兼容WHISHBONE总线的LED数码管显示控制器设计

1 引言

显示器件是电子设备中不可缺少的部分,从灯泡,阴极射线管(CRT,cathode-ray tube)显示器,到发光二级管(LED,light-emitting diode),液晶显示屏(LCD,Liquid CrystalDisplay),显示器件的发展伴随着电子技术的不断发展。目前,在小型便携式电子设备中,LED和LCD显示器件成为主要的显示器件,其中发光二级管和IJED数码管,主要用于状态指示和数字字符显示,LCD主要用于文字和图形显示。LED数码管是用发光二级管组成字符笔画或点

阵,用于显示简单字符和图形。最常用的是七段LED数码管,它用发光二级管组成数字字符8的七段笔画,至少可以显示十六进制数字的十六个字符,再加上一个小数点显示,常用于在电子设备上显示数字字符串。其特点主要在于使用简单,价格低廉,显示亮度高,功耗小。器件可靠性很高。 在中小规模集成电路的系统设计中,有专用的IED译码集成电路可以使用。在片上系统(SOC,System OnChip)的设计过程中,也会经常用到LED显示控制器,但都是根据应用需求单独设计,可重用性差。本文设计的LED数码管显示控制器就是用于控制多位LED数码管进行扫描显示的一个IP核,并且兼容WISHBONE总线,提高了IP核设计的可重用性,可以方便移植到任何使用WISHBONE总线的系统中。

2 WISHBONE总线简介

WISHBONE总线[1],全称WISHBONE片上系统互联结构,是一种主要用于片上系统(SOC,Sys-tem 0n Chip)的总线标准。最初是由Silicore公司提出的。现在已被移交给开源组织OpenCores维护。它因结构极其简单、灵活、可移植性好,又完全公开、完全免费,在SOC设计领域获得众多支持,在开源社区有大量可以免费使用的兼容WISHBONE总线的IP核。

WISHBONE总线采用的是Master/Slave的构架,主、从部件通过内部互联网络进行互联,由Master来发起每次与Slave之间的数据传输。从设备只能响应总线周期。它只定义了一种总线结构--高速总线。如果是一个低速外部设备连接到总线上,则主设备或从设备可以在总线周期中插入若干等待周期来协调设备之间的速度。这样要比设计两个不同的总线接口简单。Wishbone着重定义了IP核的接口信号和总线周期标准以实现IP核的重用,对于主从部件的互联网络,它可以实现点到点(point-to-point)、数据流(dataflow)、共享总线(shared bus)、交叉开关(crossbarswitch)四种不同结构形式。用户必须根据具体情况对协议标准进行扩展和详细设计,定义数据和地址宽度,数据顺序和标签的意义。其它的许多特性都可以由用户自行添加,从这个意义上说,Wishbone更像是给出了一个框架,等待用户提出具体的实现方法和规范。Wishbone总线的主要特征概括如下:

所有应用使用一个总线体系结构:

简单、紧凑的体系结构;

支持多控制器:

64位地址空间:

8~64位数据总线(可扩展);

支持三种总线周期:单次读写,块读写和RMW(READ-MODIFY-WRITE)总线周期;

支持重试:

提供为慢速设备使用而扼制数据流的机制:

用户自定义标签,确定数据传输类型;

用户自定义仲裁方式。

3 LED数码管显示控制器设计

3.1功能及其主要特点

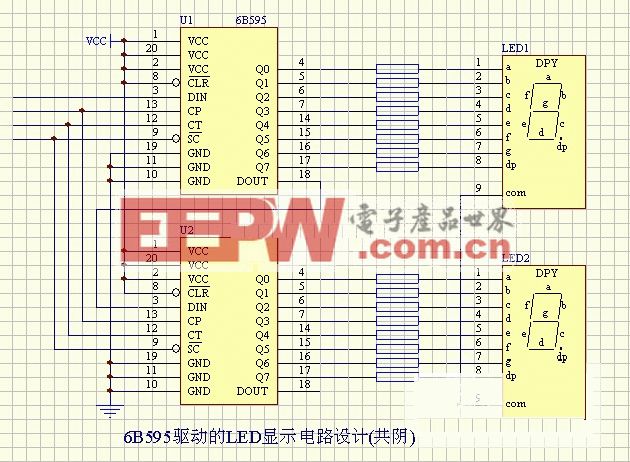

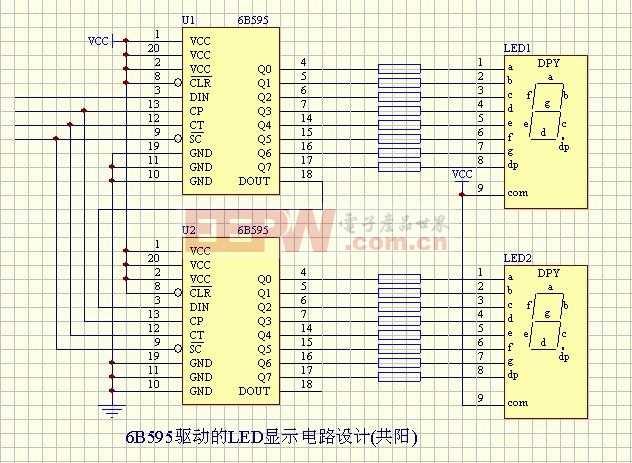

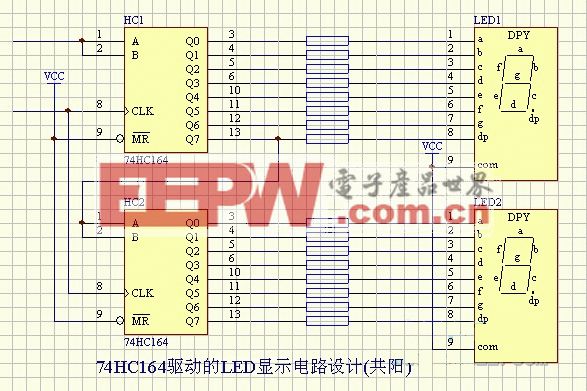

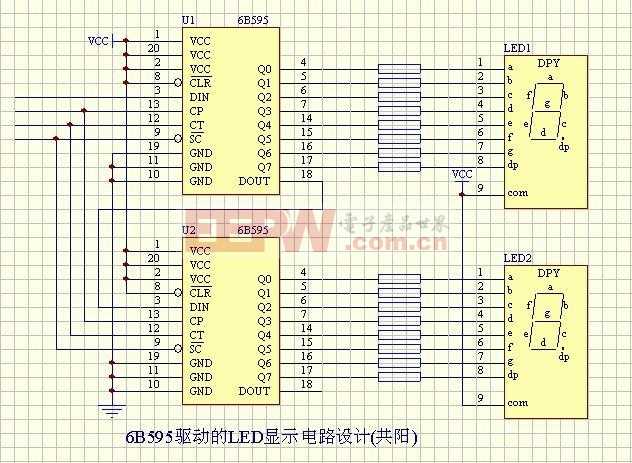

LED数码管的显示控制方式有扫描控制和独立控制两种方式。前者用于多位LED数码管并列显示的情况下,共用段控信号,通过扫描位控信号,实现分时显示。由于人眼的视觉暂留现象,形成多位LED数码管同时并列显示的效果。这种方式的实现有软件实现和硬件实现两种,软件实现是由程序控制扫描过程,硬件实现是由专用芯片或逻辑电路控制扫描过程,程序只需向扫描控制电路写入控制字和各位数码管的段码或字符的BCD(Binary CodedDecimal)码即可。独立控制方式用于单独一位或位数较少的情况,由主控设备独立控制每一个数码管的段控信号和位控信号。前一种控制方式下,对于多位数码管的情况,可以有效减少连线数量,但控制过程相对复杂。后一种控制方式下显示控制方式相对简单,但不适合多位并列显示的情况。

IED数码管的段码排列如图1所示。其编码顺序为A B C D E F G Dp。

本文设计的LED显示控制IP核是一个LED数码管扫描显示控制模块。这个IP核可以同时控制8位LED数码管并列显示,每一位都可以独立控制打开或关闭,当某一位关闭时,该位将不再显示。可以接共阴或共阳的数码管,只需向IP核写入数码管类型控制位即可。为了实现显示字符的灵活性,每位显示的字符直接由段码控制。

3.2结构

该IP核的结构如图2所示。IP核包括WISHBONE总线接口,寄存器组和显示扫描控制逻辑。

WISHBONE总线接口支持16位地址总线,8位数据总线,支持单次读写,块读写,RMW总线周期。地址总线采用部分译码,取最低四位,使用16B地址空间。

3.3寄存器

IP核内部寄存器包括八个段码寄存器和两个扫描控制寄存器。寄存器列于表1。

表中WO表示该寄存器的读写方式为只写。

LED显示段码寄存器x(LED-Dx)存储一位LED数码管的段码数据(A B C D E F G Dp)。LED-Dx(n)=l,表示该段显示,LED-Dx(n)=0,表示该段熄灭。总线复位时,其内容清零,要在某位显示某一字符,需要通过总线把段码写入相应位的段码寄存器。

LED显示控制寄存器1(LED-CTRLl)存储8位LED数码管的显示开关数据,其中每一位对应一位数码管。LED-CTRLl(n)=1,表示该位显示,LED-CTRLl(n)=0,表示该位不显示,扫描控制电路会跳过该位。总线复位后其内容清零,要显示某位,应首先在该寄存器相应位写入1。

LED显示控制寄存器2(LED-CTRL2)只使用一位,存储IED数码管的类型,控制8位数码管的显示。LED-CTRL2(0)=1,表示LED数码管是共阳的,LED-CTRL2(0)=0,表示LED数码管为共阴的。总线复位后其内容清零,开始进行显示前,应首先在该寄存器写入数码管类型控制位。

3.4输入输出接口

IP核全部寄存器为只写。复位后全部清零,所以缺省情况下,IJED数码管为共阴型,8位全部不显示,每位数码管的段显示都处于熄灭状态。在开始进行显示操作前,应首先写LED数码管类型控制位,然后根据外接数码管的个数和显示需要,通过总线写控制寄存器LED-CTRLl,打开要显示的位。随后只需更新段码寄存器,就可以显示相应的字符了。

在总线频率为10MHz情况下,该IP核的显示刷新频率为52Hz,没有闪烁感觉。如果使用中,总线频率与此不同,可以修改IP核参数,使刷新频率保持在50Hz以上即可。

4仿真与综合

4.1功能仿真

通过总线,在LED-CTRL2中写入0x01,设定LED数码管的类型为共阳。在LED一CTRLl中写入0xFF.8位数码管全部打开。然后在段码寄存器LED DO一7中分别写入字符O一7的段码(小数点不显示):OxFC,Ox6O,OxDA,OxF2,Ox66,OXB6,OxBE,OXEO。在上述条件下对LED显示控制IP核进行功能仿真。仿真使用ModelSim 6.1f。

总线读写时序仿真结果如图3所示。

4.2综合

在Ahera Quartus 74l上对该IP核进行综合,目标器件选择Altera的Cyclone II EP2C70F672C6。综合结果如下:

占用资源:逻辑单元224;

寄存器94;

估计频率:279.4 MHz。

5总结

本文设计的LED数码管显示控制器IP核,已经在我们设计的采控系统中成功应用,完全达到设计要求。

在SOC的设计过程中,以IP核为基础的设计方法已经成为主流,IP核的重用是一个不可轻视的问题,而采用统一的总线接口规范是解决IP核重用问题的重要途径[3]_。本文的设计严格遵循了WISH-BONE Rev.B.3规范,在任何采用该规范设计的系统中,可以直接使用。本文的设计对可复用IP核和SOC的设计起到一定借鉴作用。

led显示器相关文章:led显示器原理

评论