有源箝位Flyback软开关电路设计

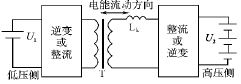

Flyback变换器由于其电路简单,在小功率场合被普遍采用。但是,由于变压器漏感的存在,引起开关管上过高的电压应力。普通的RCD嵌位Flyback变换器其漏感能量消耗在嵌位电阻R上,开关管上电压应力的大小取决于消耗在嵌位电阻上能量的大小。消耗在嵌位电阻上的能量越多,开关管的电压应力就越低,但也影响了整个变换器的效率,因此,普通的RCD嵌位Flyback变换器总存在着开关管电压应力与整个变换器效率之间的矛盾。

轻小化是目前电源产品追求的目标。而提高开关频率可以减小电感、电容等元件的体积。但是,开关频率提高的瓶颈是开关器件的开关损耗,于是软开关技术就应运而生。一般,要实现比较理想的软开关效果,都需要有一个或一个以上的辅助开关为主开关创造软开关的条件,同时希望辅助开关本身也能实现软开关。

本文介绍的一种有源嵌位Flyback软开关电路,不但能实现ZVS,而且也解决了前述的普通RCD嵌位Flyback变换器中存在的问题。

1 工作原理

1 工作原理

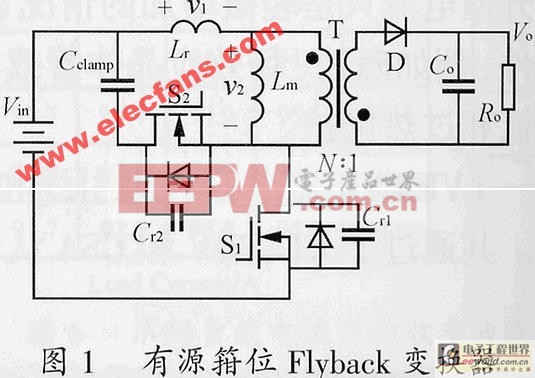

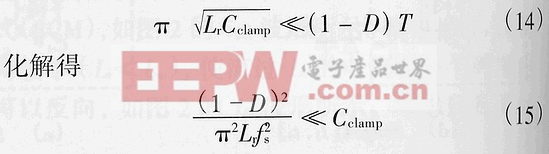

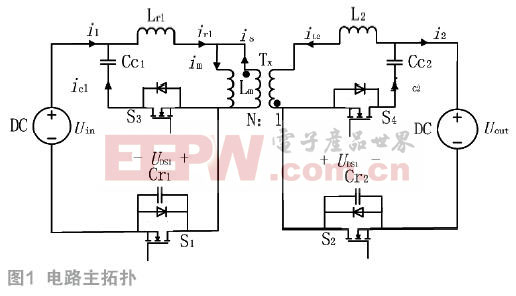

电路如图1所示,其两个开关S1及S2互补导通,中间有一定的死区以防止共态导通。变压器激磁电感Lm设计得较大,使电路工作在电流连续模式(CCM),如图2的iLm波形所示。而电感Lr设计得较小(Lr?Lm),使流过Lr的电流在一个周期内可以反向,如图2的iLr波形所示。考虑到开关的结电容以及死区时间,一个周期可以分为8个阶段,各个阶段的等效电路如图3所示。其工作原理如下。

1)阶段1〔t0,t1〕该阶段S1导通,Lm与Lr串联承受输入电压,流过Lm及Lr的电流线性上升。

V2=Vin(Lin/Lm+Lr) (1)

由于Lr?Lm,所以式(1)可简化为

V2≈Vin (2)

2)阶段2〔t1,t2〕t1时刻S1关断,Lm及Lr上的电流给S1的输出结电容Cr1充电,同时使S2的输出结电容Cr2放电。t2时刻S2的漏源电压下降到零,该阶段结束。

图2

3)阶段3〔t2,t3〕当S2的漏源电压下降到零之后,S2的寄生二极管就导通,将S2的漏源电压箝位在零电压状态。Lr和Lm串联与嵌位电容Cclamp谐振,Cclamp上电压vc缓慢上升,v2上电压也缓慢上升。

图2

3)阶段3〔t2,t3〕当S2的漏源电压下降到零之后,S2的寄生二极管就导通,将S2的漏源电压箝位在零电压状态。Lr和Lm串联与嵌位电容Cclamp谐振,Cclamp上电压vc缓慢上升,v2上电压也缓慢上升。

v2=(Lm/Lm+Lr)vc (3)

4)阶段4〔t3,t4〕t3时刻S2的门极变为高电平,S2零电压开通。流过寄生二极管的电流流经S2。此时间段依然维持Lr和Lm串联与嵌位电容Cclamp谐振,v2缓慢上升。

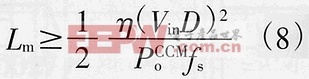

5)阶段5〔t4,t5〕t4时刻v2上升到一定的电压使副边二极管D导通,v2被嵌位在-NVo。Lr与Cclamp谐振。在保证t5时刻Lr电流反向的情况下,其谐振周期应该满足

式中:toff为主开关管S1一个周期内的关断时间。

图3

t5时刻S2关断,该阶段结束。

图3

t5时刻S2关断,该阶段结束。

6)阶段6〔t5,t6〕t5时刻Lr上的电流方向为负,此电流一部分使S1的输出结电容Cr1放电,另一部分对S2的输出结电容Cr2充电。t6时刻S1的漏源电压下降到零,该阶段结束。

7)阶段7〔t6,t7〕当S1的漏源电压下降到零之后,S1的寄生二极管就导通,将S1的漏源电压箝在零电压状态,也就为S1的零电压导通创造了条件。此时,Lr上的承受电压v1为

v1=Vin+NVo (5)

Lr上电流快速上升。流过副边整流二极管D电流iD则快速下降。

diD/dt=-N[Vin+NVo]/Lr+NVo/Lm) (6)

考虑到Lr?Lm,式(6)可简化为

diD/dt=-N(Vin+NVo)/Lr (7)

8)阶段8〔t7,t8〕t7时刻S1的门极变为高电平,S1零电压开通,流过寄生二极管的电流流经S1。t8时刻副边整流二极管D电流下降到零,D自然关断,电路开始进入下一个周期。

可以看到,在这种方案下,两个开关S1和S2实现了零电压开通,二极管D自然关断。

2 软开关的参数设计

假定电路工作在CCM状态。由于S2的软开关实现是Lr与Lm联合对Cr1及Cr2充?电,而S1的软开关实现是单独的Lr对Cr1及Cr2充放电。因此,S2的软开关实现比较容易,而S1的软开关实现相对来说要难得多。所以,在参数设计中,关键是要考虑S1的软开关条件。

电流连续模式有源嵌位Flyback变换器ZVS设计步骤如下所述。

2.1 变压器激磁电感Lm的设定

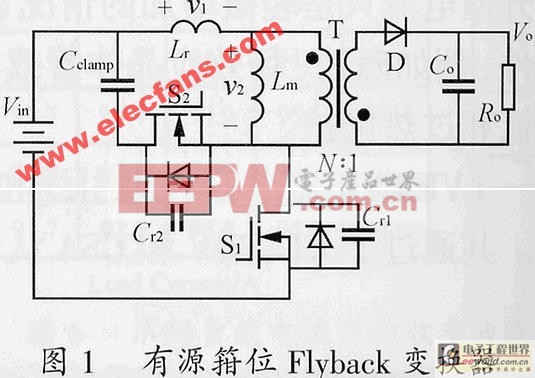

由于Lr的存在,变换器的有效占空比Deff(根据激磁电感Lm的充放电时间定义,见图2)要小于S1的占空比D,但是由于t5~t8时刻iLr的上升速度非常的快,所以可近似地认为Deff=D。这样,根据Flyback电路工作在CCM条件,则

式中:η为变换器效率;

fs为开关频率;

PoCCM为变换器的输出功率。

在实际设计中,为了保证电路在轻载时也能工作在电流连续模式,Lm一般取为

2.2 电感Lr的设定

为了实现S1的ZVS,t5时刻储存在Lr内的能量足以令S1的输出结电容Cr1放电到零,同时使S2的输出结电容Cr2充电到最大。即

式中:vds=vds1=vds2≈Vin+NVo;

式中:vds=vds1=vds2≈Vin+NVo;

Cr=Cr1+Cr2。

根据式(4)取定合适的谐振周期可以令

2.3 电容Cclamp的设定

2.3 电容Cclamp的设定

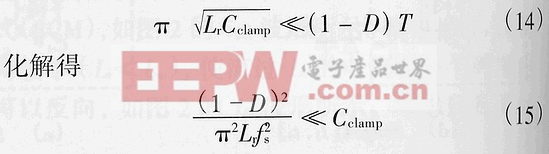

根据式(4)有

在满足式(15)的前提下,取定合适的Cclamp令iLrmax=iLrmin。

在满足式(15)的前提下,取定合适的Cclamp令iLrmax=iLrmin。

2.4 死区时间的确定

为了实现S1的ZVS,必须保证在t6到t7时间内,S1开始导通。否则Lr上电流反向,重新对Cr1充电,这样S1的ZVS条件就会丢失。因此,S2关断后、S1开通前的死区时间设定对S1的ZVS实现至关重要。合适的死区时间为电感Lr与S1及S2的输出结电容谐振周期的1/4,即

严格地讲,开关管输出结电容是所受电压的函数,为方便起见,在此假设Cr1与Cr2恒定。

2.5 有效占空比Deff的计算

有效占空比Deff比开关管S1的占空比D略小。

Deff=D-ΔD(17)

[(Vin+NVo)/Lr]ΔDT≈2(P/DVin) (18)

ΔD≈2PLrfs/DVin(Vin+NVo) (19)

代入式(17)得

Deff=D-2PLrfs/(DVin(Vin+NV0) (20)

2.6 开关管电压应力计算

Vs1,s2≈Vin+NVo+(2PLrfs/DVin(1-D) (21)

式(21)中第三项相对来说较小,故开关管的电压应力接近于Vin+NVo。

3 实验结果

3 实验结果

为了验证上述ZVS的实现方法,设计了一个实验电路,其规格及主要参数如下:

输入电压Vin48V;

输出电压Vo12V;

输出电流Io0~5A;

工作频率f100kHz;

主开关S1及S2IRF640;

变压器激磁电感Lm144μH;

变压器原副边匝数比n=N8/3;

电感Lr10μH;

电容Cclamp2μF。

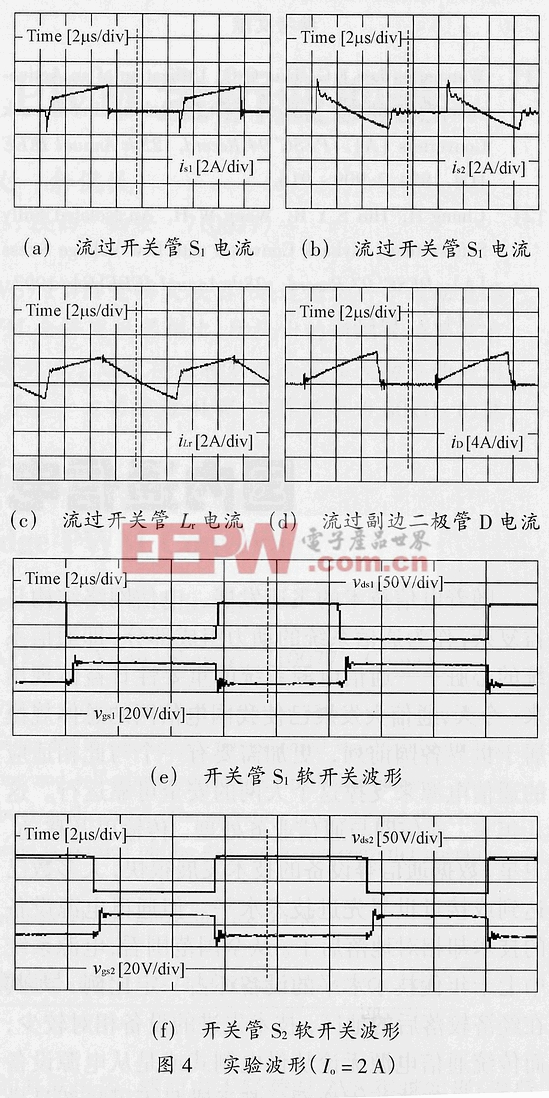

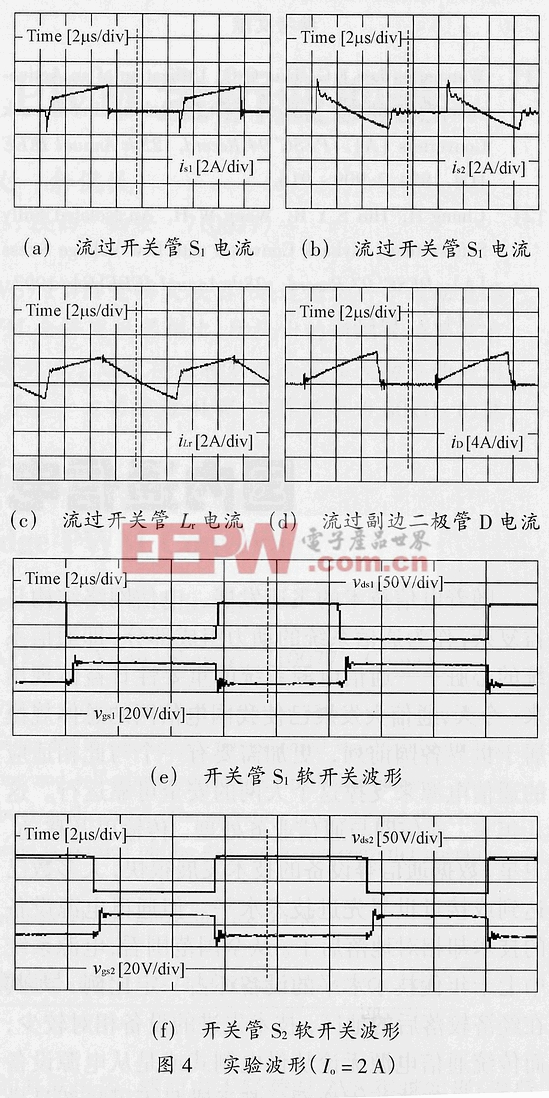

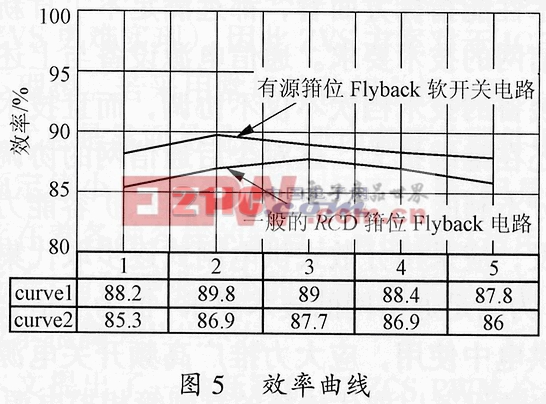

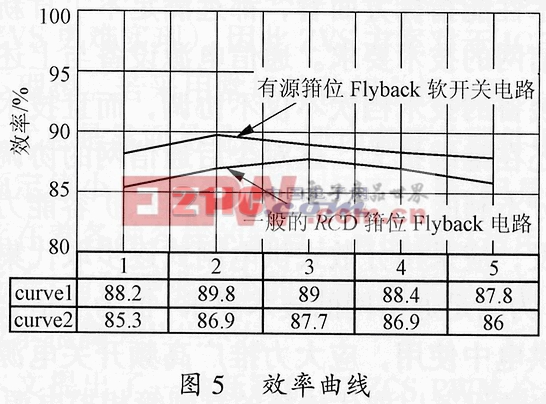

图4给出的是负载电流Io=2A时的实验波形。从图4(e)及图4(f)可以看到,S1和S2都实现了ZVS。图5给出了两种Flyback电路的效率曲线,可以看到,有源嵌位Flyback软开关电路有效地提升了变换器的效率。

4 结语

4 结语

有源嵌位Flyback软开关电路在实现主开关及辅助开关ZVS的同时,也实现了输出整流二极管的自然关断,因此,有效地减少了开关损耗,提高了变换器效率。另外,它也大大地降低了开关管的电压应力,这从实验波形中可以看得比较清楚。

评论