51系列I/O口上拉电阻使用点滴

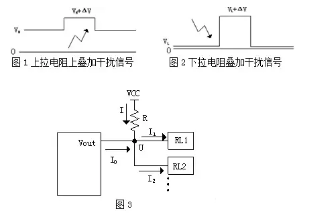

按常规,在51端口(P1、P2、P3)某位用作输入时,必须先向对应的锁存器写入1,使FET截止。一般情况是这样,也有例外。所谓IO口内部与电源相连的上拉电阻而非一常规线性电阻,实质上,该电阻是由两个场效应管并联在一起:一个FET为负载管,其阻值固定;另一个FET可工作在导通或截止两种状态(姑且叫可变FET)。使其总电阻值变化近似为0或阻值较大(20千欧--40千欧)两种情况。当和端口锁存器相连的FET由导通至截止时,该阻值近似为0,可将引脚快速上拉至高电平;当和锁存器相连的FET由截止至导通时,该电阻呈现较大阻值,限制了和端口锁存器相连的FET的导通电流。

51I/O口作为输入端和外部信号相连有时必须考虑上述特性,本人在设计LTP1245热敏打印头驱动板时,资料上推介热敏头“抬头”和“纸尽”信号由头中内嵌检测电路提供,MCU IO口采集该信号时需加缓冲(如74HC04)。当时本人认为51IO口上拉电阻为一较大阻值的固定电阻,对 输入信号无影响,故未加缓冲电路(为降低成本能省则省)。可到调试PCBA时发现,“抬头”、“纸尽”状态变化时,采集信号只在3.90V--5.10V之间变化,应为低电平时无低电平输出。究其原因,打印头的“抬头”、“缺纸”信号输出为一光敏三极管的集电极输出,集电极和电源间原有一个负载电阻,饱和导通设计工作电流仅为450--1100微安,当该集电极直接和MCU IO口某位相连时,IO口上拉电阻和光敏三极管负载电阻并联,当IO口上拉时,上拉电阻极小致使光敏三极管直流负载线斜率陡然增大,工作状态进入放大区而非希望的饱和区。当时在不改硬件的条件下,我几乎无计可施,甚至想到了准备烧断IO口上拉电阻(前两天我曾发帖求救怎么烧断IO口上拉电阻的方法)后来听网友建议该方法风险较大,所以总想用软件方法解决。

后来我的解决方法是:采样信号前不是先向对应锁存器写1,而是先写入0,再写入1,延时约10毫秒以上,然后再采样(当然此法只适应于采样频率很低的情况)。这样作的目的是:先写入0迫使IO口上拉电阻先为一较大值,此时如果外部光敏三极管本来处于截止状态,当完成上述一系列锁存器的写入过程后光敏管仍为截止态,IO口正确采样到高电平;此时如果外部光敏三极管基极电流足够大有容许三极管饱和导通的条件(即基极吸收到充分光强),虽然采样一开始集电极被人为钳位在低电平,但当下一时隙和IO口相连的锁存器被写入1时,在IO口上拉电阻中的可变FET导通之前,光敏三极管已先进入饱和态而又把引脚钳位在实际输出的低电平,此时MCU IO口的上拉电阻仍为较大阻值,同时和原光敏三极管集电极负载电阻并联(考虑并联后阻值变化,原光敏三极管集电极负载电阻需增大到适当阻值)充当饱和导通后光敏三极管的负载电阻,事实上,IO口上拉电阻中的可变FET未来得及导通又被截止了,由此又保证了信号低电平的正确采样。经过波形测试问题得。

手机电池相关文章:手机电池修复

评论