S3C2410外围存储系统的研究与设计

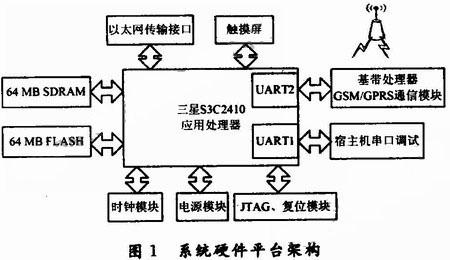

Samsung公司推出的基于ARM920T内核的16/32位RISC微处理器S3C2410,为手持设备和一般类型应用提供了低价格、低功耗、高性能小型微控制器的解决方案。为了降低整个系统的成本,S3C2410提供了丰富的内部设备。其中加强的ARM体系结构MMU用于支持WinCE,EPOC32和Linux。随着技术的进步和发展,电子产品的功能日益强大,而嵌入式操作系统可以有效地管理各项功能,并且能够缩短产品开发周期,因此将微处理器与嵌入式操作系统进行联合开发成为一种趋势,然而微处理器的片内存储资源有限,若要进行嵌入式系统的移植,必须扩展其存储系统。对于嵌入式系统的开发人员来说,深入理解其存储系统原理和有效地管理存储系统对正确高效地设计嵌入式系统的硬件和底层软件编程具有重要的意义[1]。

1 S3C2410的寻址原理

ARM920T内核提供了32位的地址总线,可以访问4G(232)的线性地址空间,而S3C2410的内部地址总线是30bit(HADDR[29:0]),能够访问的最大外部地址空间是230,即1G的地址空间0x00000000~0x3FFFFFFFF,可见S3C2410仅利用了ARM920T的32位地址总线的低30位,并且是一一对应相连的[1]。由表1可知S3C2410将1G的外部地址空间分成了8个存储器组,每个组的大小为128M,其中6个用于ROM、SRAM等存储器,2个用于ROM、SRAM、SDRAM等存储器。基于芯片体积及成本的考虑,当S3C2410对外寻址时,采用了部分译码的方式,即低位地址线用于外围存储器的片内寻址,而高位地址线用于外围存储器的片外寻址。如表1所示,由于每个存储器组的起始地址及空间大小固定,对于系统要访问的任意外部地址,S3C2410可以方便地利用内部地址总线的高3位HADDR[29:27]来选择该地址属于哪一个存储器组(Bank),从而激活相应的Bank选择信号,并且使用外部地址总线A[26:0]来实现相应Bank的内部寻址,寻址范围为128M(227),从而使得其外围地址访问空间为1GB(128MB×8)。S3C2410正是通过这种机制来完成外部地址空间的寻址全过程。

S3C2410访问SDRAM地址空间的过程比较难理解,这主要和SDRAM的存储结构有关。为了更深入地理解其寻址机制,笔者以SDRAM芯片HY57V561620B(32MB)为例进行详细地说明。该芯片的内部存储结构是4Banks×4M×16Bit,即共有4个Bank,每个Bank中有4M个半字(16Bit)。Bank地址可以通过BA[1:0]与地址总线的高位相连来确定,具体BA[1:0]与哪个地址位相连,不同的SDRAM存储系统有不同的方案,详见参考文献[3]。而每个Bank中的存储单元由行地址和列地址来唯一标识[1],该芯片通过行地址锁存引脚nRAS和列地址锁存引脚nCAS分别与S3C2410的引脚nSRAS(SDRAM行地址选通信号)和nSCAS(SDRAM列地址选通信号)连接,从地址总线获得行地址和列地址。而且列地址的位数可以在BANKCONn(n=6,7)的中的SCAN——BANKCONn [1:0]来配置,00=8-bit,01=9-bit,10=10-bit,其复位值为00,即8bit。

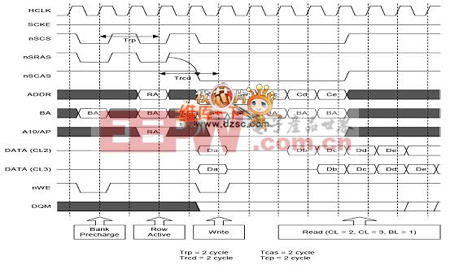

在实际工作中,如图1所示,在第3个总线时钟,nSCS为低电平,表示SDRAM被选中,并且地址线的Bank地址与相应的行地址同时发出,这个命令称之为“行有效”或“行激活”(Row Active)。此时SDRAM将行地址锁存(nSRAS有效),但还没有执行写命令(nWE为高电平),因为没有列地址(nSCAS为高电平),存储单元无法确定。经过Trcd(RAS至CAS延迟)后,SDRAM再次被选中(nSCS为低电平),此时nSCAS为低电平,指示SDRAM此时地址线上的地址为列地址,同时nWE有效,写操作被执行。可见发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址,相关的列地址被选中之后,将会触发数据传输。至此,S3C2410对SDRAM的寻址就完成了。可见,S3C2410将地址总线上的地址分成行地址和列地址并分开传输给SDRAM。基于上述的寻址机制,由BA[1:0]和12根地址线就可以寻址32M或更大的地址空间了。

图 1 S3C2410 SDRAM时序图

2 存储器控制器和相关引脚介绍

2.1寄存器介绍

S3C2410存储器控制器主要有:总线带宽和等待控制寄存器(BWSCON);总线控制寄存器(BANKCONN:nGCS0-nGCS5);BANK控制寄存器(BANKCONn:nGCS6-nGCS7);刷新控制寄存器(REFRESH);BANKSIZE寄存器;SDRAM模式寄存器集寄存器(MRSR)等,详情请见参考文献[3]。

2.2相关引脚

S3C2410提供了相关的引脚来控制存储器访问:

组选择信号:nGCS0-nGCS5,nGCS6(nSCS0),nGCS7(nSCS1)引脚用来选择相应的存储器组。

访问控制信号:为了实现ARM存储器访问指令LDR/STR字节、半字和字访问的三种方式,在S3C2410的存储器组中,除了Bank0以外的所有地址空间都可以通过编程设置为8位、16位或32位对准访问,Bank0可以设置为16位或32位。引脚nWBE[3:0](写字节使能)实现8bit ROM芯片组的三种访问方式,或者SRAM不使用UB/LB(在BWSCON中设置)的情况下,与UB/LB连接。引脚nBE[3:0](在使用SRAM情况下的字节允许信号)在SRAM使用UB/LB(是否使用可在BWSCON中设置)的情况下与UB/LB连接。DQM[3:0](SDRAM数据屏蔽信号)引脚实现对SDRAM的三种访问。还有nWAIT、nXBREQ/nXBACK引脚。

存储器相关文章:存储器原理

评论