基于ZigBee协议无线抄表智能电网终端设计

1 ZigBee协议分析

ZigBee协议栈依次从最底层开始由物理层、数据链路层、网络层和应用层组成,其中物理层和数据链路层由IEEE 802.15.4工作组制定,网络层和应用层(APL)由ZigBee联盟制定。物理层定义了3种流量等级:当频率采用868 MHz时,提供20 Kb/s的传输速率;当采用915MHz时,提供40 Kb/s的传输速率;当采用2.4 GHz时,能够提供250 Kb/s的传输速率,在我国采用的是这种免费频段。数据链路层可分为逻辑链路控制子层(LLC)和介质访问控制子层(MAC),其功能包括数据包的分段与重组,数据包的顺序传输,无线链路的建立、维护和拆除,确认模式的帧传送和接收,信道接入控制、帧校验、预留时隙管理和广播信息管理等。网络层的功能包括拓扑管理、MAC管理、路由管理和安全管理。应用层是协议栈的最上层定义了各种类型的应用业务。该系统中主要涉及ZigBee网路中数据采集终端节点的设计,也可作为网络路由器应用。

2 无线抄表数据收发终端总体设计

RS 485总线具有很强的抗共模干扰能力,可以进行多点和双向通信,允许在一对双绞线上驱动一个或多个设备,这样就可以实现一个收发器管理多个用户电表。基于RS 485总线电表简单易操作,成本低,市场上很多都是采用RS 485智能电表,该系统可以广泛应用。无线Zig-Bee模块通过SPI接口接收来自微控制器系统的数据信号,将数据信号发送出去。

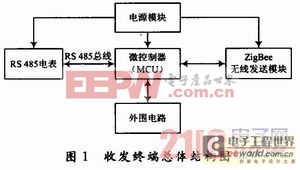

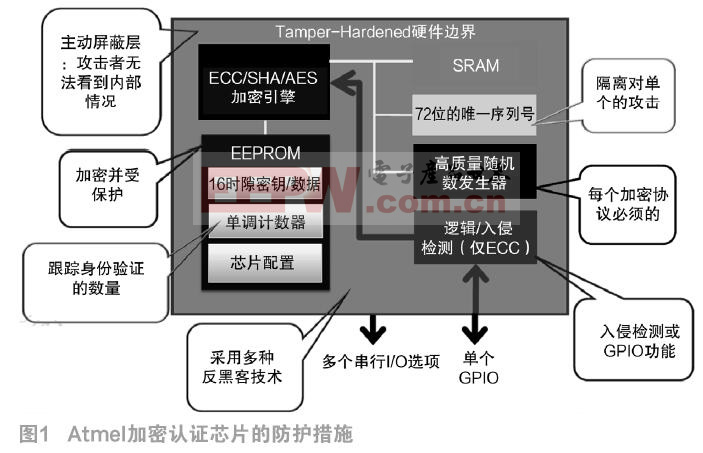

无线抄表数据收发终端在整个抄表系统中扮演的是路由和终端的角色,是一种全功能设备FFD(Full Function Device)。该系统总体设计思路是:通过RS 485总线将电表数据收集,然后通过MCU电路处理,通过RS 232,SPI接口发送到ZigBee无线通信模,块,最后利用无线通信模块发送到路由器节点或网络协调器。系统的总体结构如图1所示。

3 收发终端硬件设计

该终端系统主要包括:电表数据收集电路、无线发送电路和电源电路3部分。

(1)电表数据收集电路主要是MCU控制电路,处理RS 485发送过来的数据。主要有MCU芯片,RS 485控制芯片、光耦隔离器、时钟电路、稳压电路等构成。

(2)无线发送电路主要是通过SPI接口接收MCU的处理数据,通过RF射频天线发送。

(3)电源电路主要是完成将交流220 V电压转化成直流电压,再通过稳压等完成对系统的供电。主要由小型变压器、热敏电阻、压敏电阻器、稳压芯片等构成。

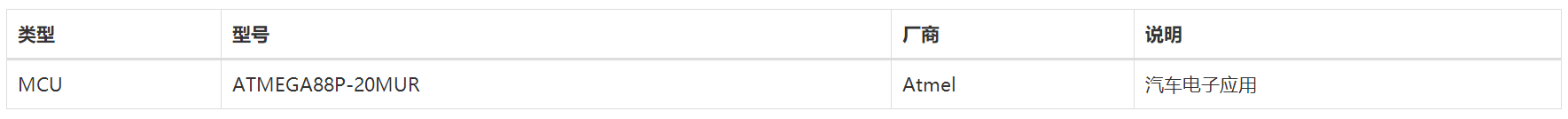

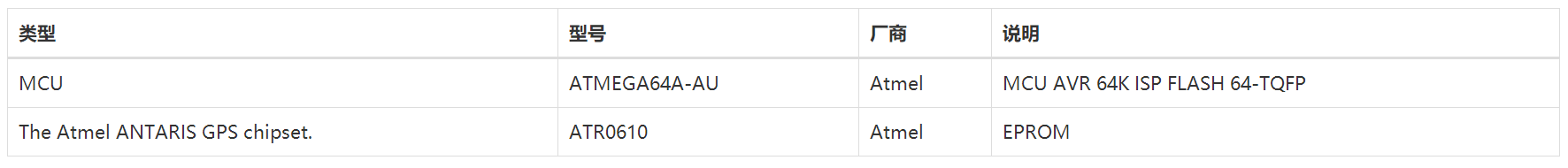

系统主要器件选型:

MCU:选用Ateml公司的ATmega 64L芯片,是一款基于支持实时仿真的高性能、低功耗的8位RISC结构的AVR微控制器。带有64 KB系统内可编程FLASH,4 KB的片内SRAM,64 KB可选外部存储空间,32个通用寄存器,实时计数器(RTC),4个具有比较模式与PWM的灵活定时器/计数器(T/C),2个USART,面向字节的两线串行接口,8路10位具有可选查分输入级可编程增益的ADC,看门狗定时器,一个SPI接口,JTAG接口,以及6个可以通过软件进行选择的省电模式,满足无线抄表系统中对可靠性和功耗的要求。

ZigBee芯片:选用TI公司的CC2430 RF,其是一颗真正的系统芯片,提倡CMOS解决方案,这种解决方案能够提高性能并能满足以ZigBee为基础的2.4GHz ISM免费波段的应用,同时满足低成本,低功耗的要求。它结合一个高性能2.4 GHz DSSS(直接序列扩频)射频收发器核心和一颗工业级小巧高效的8051控制器,收发波特率250 Kb/s。CC2430在接收和发射模式下,电流损耗分别为27 mA或25 mA。CC2430的休眠模式和转换到主动模式的超短时间的特性,特别适合无线抄表这种要求电池寿命比较长的应用。接收数据时,当CC2430全部收到帧开始定界符SFD后,IRQ_SFD(中断标志位寄存器)置1;当RXFIFO中有数据时,RFSTATUS.FIFO置1,数据为空时,置0;当RXFIFO中未读过的字节超过编程设置在IOCFG0.FIFOP_THRRF_P的阈值时,RFSTATUS.FIFOP置1,反之,置0。RF_N两个引脚显示接收和发送数据状态,RF_P引脚:接收时,正RF(射频)输入信号到LNA(低噪声放大器);发送时,接收来自PA(功率放大器)的正RF(射频)信号。RF_N引脚:接收时,负RF(射频)输入信号到LNA(低噪声放大器);发送时,接收来自PA(功率放大器)的负RF(射频)信号。CC2430通过SPI接口接收ATmega64L的时钟信号和片选信号,由内部集成的8051核完成数据信号的处理和输入/输出操作,从而完成电表数据的传输。

片外FLASH:用来存储电表数据,选用金士顿1 GB SD卡,由于电源电路的输出电压为5 V,而SD卡需3.3 V供电,所以要将电压转换,用SE8117T33输出3.3 V电压,接到SD卡VDD引脚上。

时钟芯片:选用Philips公司的实时时钟芯片PCF8563T,是一种低功耗CMOS时钟芯片,提供一个可编程输出、终端输出和掉电检测器,所有地址和数据都通过I2C总线接口串行传输,得到最大的总线传输速度。

评论