高动态范围有源混频器ADRF6655

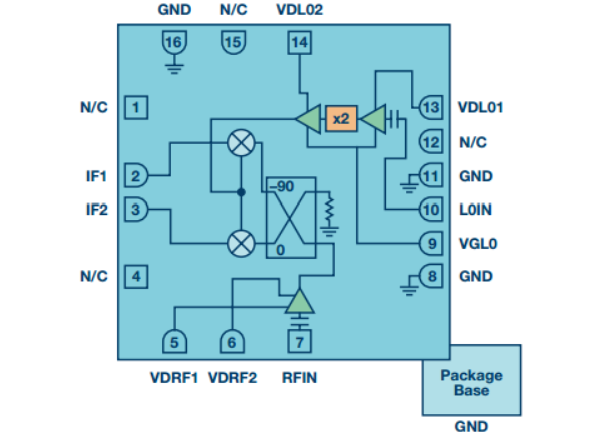

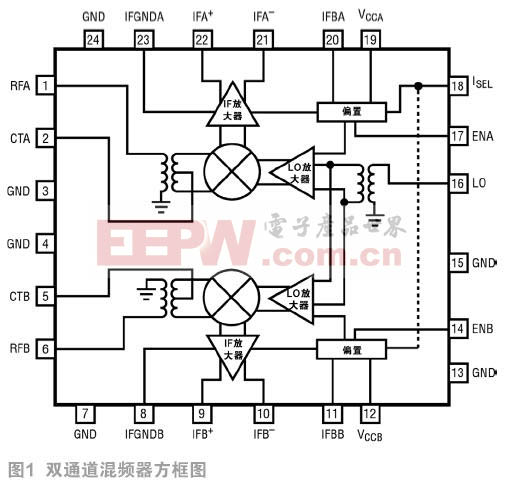

ADRF6655是一款高动态范围有源混频器,集成PLL和VCO。频率合成器利用可编程整数N分频/小数N分频PLL产生本振输入,供给混频器。PLL基准输入标称值为20 MHz。基准输入可以进行分频或倍频,然后施加于PLL鉴相器。PLL支持10 MHz至160 MHz范围内的输入基准频率。鉴相器输出控制一个电荷泵,其输出在片外环路滤波器中进行积分。然后,环路滤波器输出施加于一个集成式VCO。VCO输出(2 × fLO)再施加于一个本振(LO)分频器和一个可编程PLL分频器。

可编程分频器由一个Σ-Δ调制器(SDM)进行控制。SDM的模数可以在1至2047范围内编程。

该宽带有源混频器采用一个偏置调整电路,允许通过提高电源电流来增强IP3性能。在典型条件下,该混频器的输入IP3超过25 dBm,单边带噪声系数(NF)为12 dB。电源电流增大约20 mA时,IIP3可提升至约29 dBm。采用200 Ω差分IF输出阻抗时,典型电压转换增益为6 dB。IF输出可以外部匹配,以支持有限频率范围内的上变频。

ADRF6655采用先进的硅-锗BiCMOS工艺制造,提供40引脚、裸露焊盘、无铅、6 mm × 6 mm LFCSP封装,额定温度范围为−40°C至+85°C。

特性

评论