采样时钟抖动对ADC信噪比的影响及抖动时钟电路

ADC是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了接收机的整体性能。在A/D转换过程中引入的噪声来源较多,主要包括热噪声、ADC电源的纹波、参考电平的纹波、采样时钟抖动引起的相位噪声以及量化错误引起的噪声等。除由量化错误引入的噪声不可避免外,可以采取许多措施以减小到达ADC前的噪声功率,如采用噪声性能较好的放大器、合理的电路布局、合理设计采样时钟产生电路、合理设计ADC的供电以及采用退耦电容等。

本文主要讨论采样时钟抖动对ADC信噪比性能的影响以及低抖动采样时钟电路的设计。

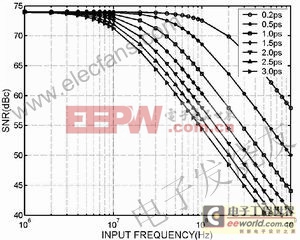

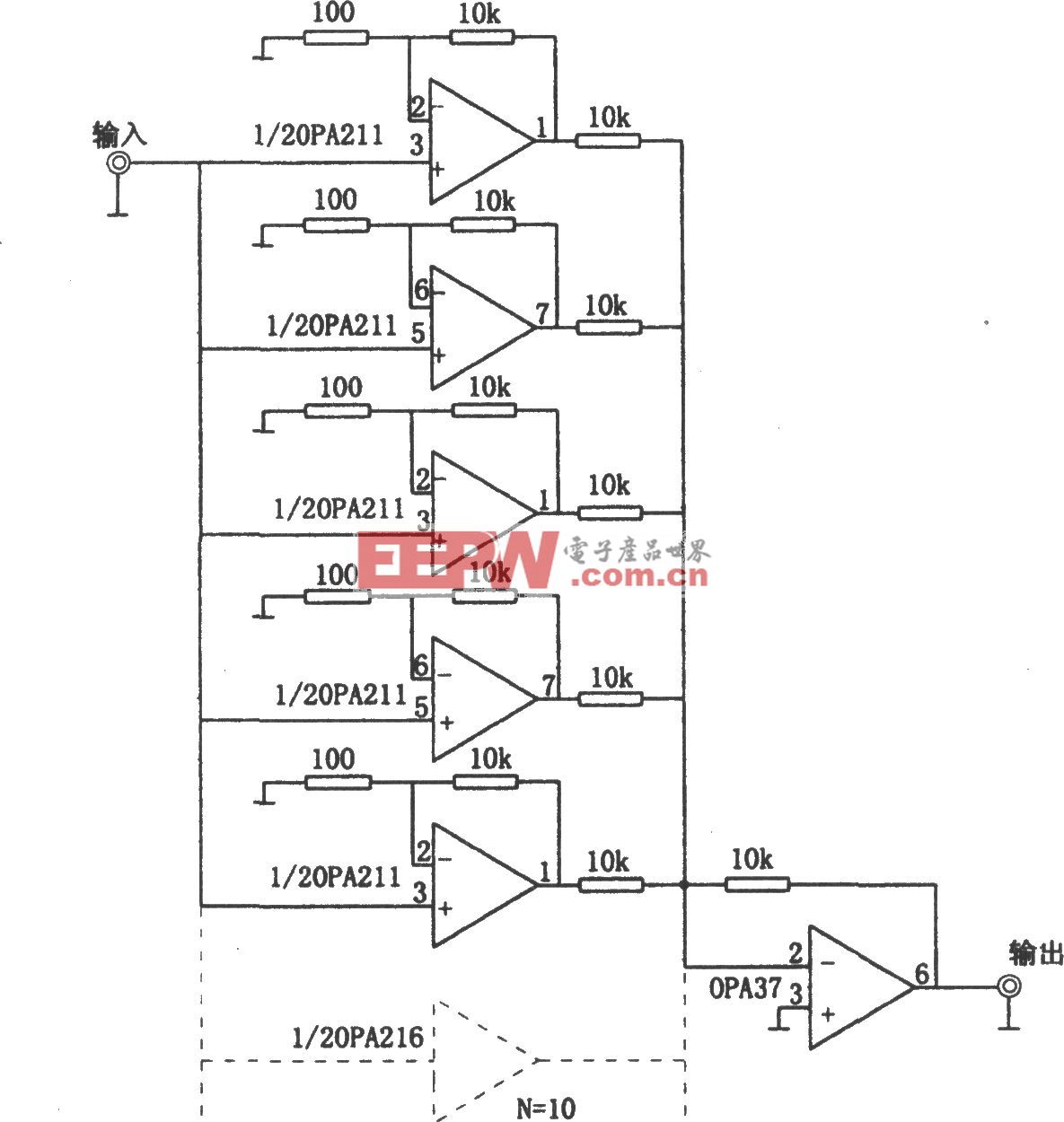

(a)12位ADC理想信噪比

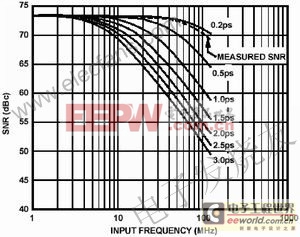

(b)AD9245实测信噪比

图1 不同时钟抖动情形下12位ADC的信噪比示意图

时钟抖动对ADC信噪比的影响

采样时钟的抖动是一个短期的、非积累性变量,表示数字信号的实际定时位置与其理想位置的时间偏差。时钟源产生的抖动会使ADC的内部电路错误地触发采样时间,结果造成模拟输入信号在幅度上的误采样,从而恶化ADC的信噪比。欢迎转载,本文来自电子发烧友网(http://www.elecfans.com)

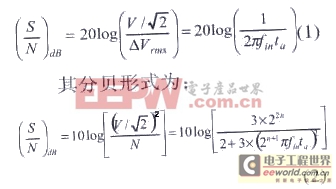

在时钟抖动给定时,可以利用下面的公式计算出ADC的最大信噪比:

根据公式(2),图1分别给出了量化位数为12-bit时不同时钟抖动情形下ADC理想信噪比和实测信噪比示意图。

由图1可以看出时钟的抖动对ADC信噪比性能的恶化影响是十分明显的,相同时种抖动情形下进入到ADC的信号频率越高,其性能恶化就越大,同一输入信号频率情形下,采样时钟抖动越大,则ADC信噪比性能恶化也越大。对比图1中两个示意图可以看出实测的采样时钟抖动对ADC信噪比性能的影响同理论分析得到的结果是十分吻合的,这也证明了理论分析的正确性。因此,在实际应用时不能完全依据理想的信噪比公式来选择A/D转换芯片,而应该参考芯片制造商给出的实测性能曲线和所设计的采样时钟的抖动性能来合理选择适合设计需要的A/D转换芯片,并留出一定的设计裕量。

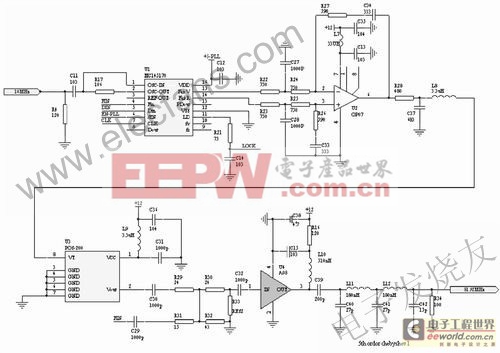

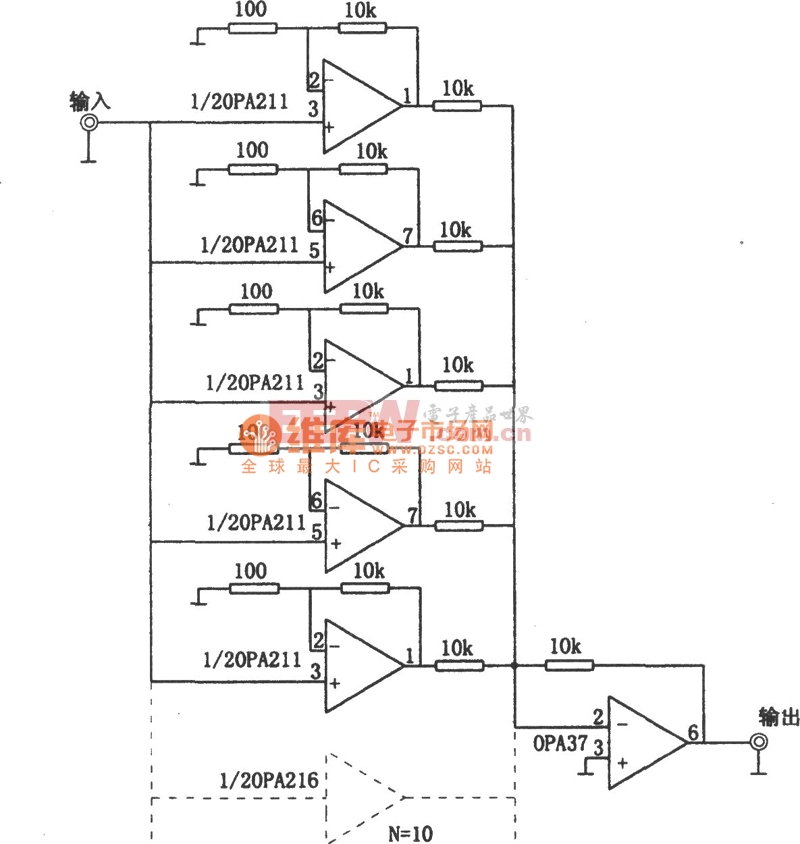

图2 一个实用的低抖动时钟产生电路

评论