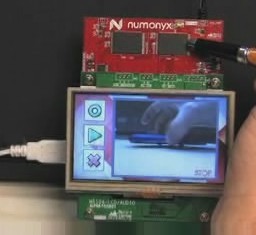

可应用三维存储结构PCM的高集成NAND型相变内存方案

日本中央大学理工学部电气电子信息通信工学科教授竹内健等人的研发小组提出了NAND型相变内存(Phase Change Memory:PCM)方案,并在2012年5月20~23日于意大利米兰举行的“International Memory Workshop(IMW)”上发表。这种内存的选择元件采用多晶硅MOS晶体管,这样就可以采用无需触点的简洁式NAND型闪存的存储器单元结构,理论上,存储器单元的面积可降至4F2,而且还可以减少工序数。竹内教授认为,该技术可应用于以“BiCS(Bit-Cost Scalable)”为代表的“采用三维存储器单元结构的PCM等”(竹内)。

传统PCM采用的RAM接口,存在RESET时间在10ns级、而SET时间却在100ns级的课题。SET时间较长会对读取性能有所制约,而且能耗也会增大。

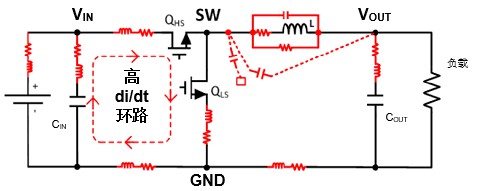

因此,中央大学的竹内教授等人没有将PCM用作RAM,而是像NAND型闪存那样用来进行区块擦除等。将耗时较长的SET操作作为数据擦除使用,在使区块内所有单元同时初始化的“区块擦除”时使用。然后将高速的RESET操作用做写入操作。据介绍,采用这种方式后,与性能因SET操作时间较长而受到制约的传统RAM接口相比,写入速度可提高至7.7倍,能耗最大可削减70%。竹内表示,将PCM “应用于区块擦除时,即使在同时擦除两个存储器单元的情况下,其能耗也不会达到2倍”。通过采用这种操作方式,可轻松将PCM用于存储应用。但另一方面,这种方式无法进行随机存取。

NAND型PCM的课题是,采用NAND串后容易出现写入干扰。据介绍,要想写入时不产生干扰,就需要将通道晶体管(Pass Transistor)的通态电流至少提高至最小RESET电流的4倍以上,将RESET电压提高至1.07倍以上。

评论