运算放大器--单通道、双通道、四通道优缺点及结构

封装引脚输出

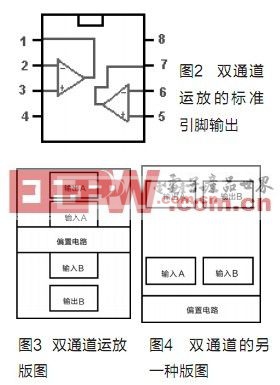

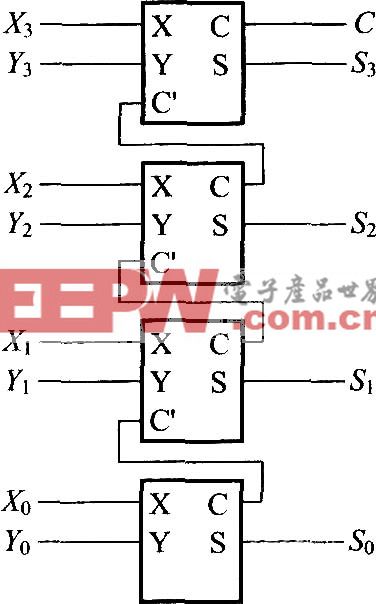

图1中的版图对单通道运放来说完全没有问题,但对双通道运放来说问题就出现了。双通道运放的标准引脚输出如图2所示。

图3是双通道运放在晶体管级的一种可能的底层规划图。这里有个问题:通道B的输出必须越过输入线才能到达引脚7。在很早以前,双极性模拟工艺还是采用的单层金属化工艺,必须使用穿接(cross-under)方法,因此对性能会有影响。

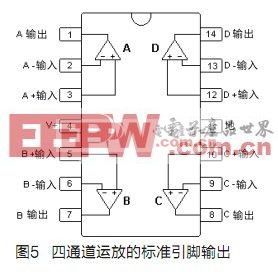

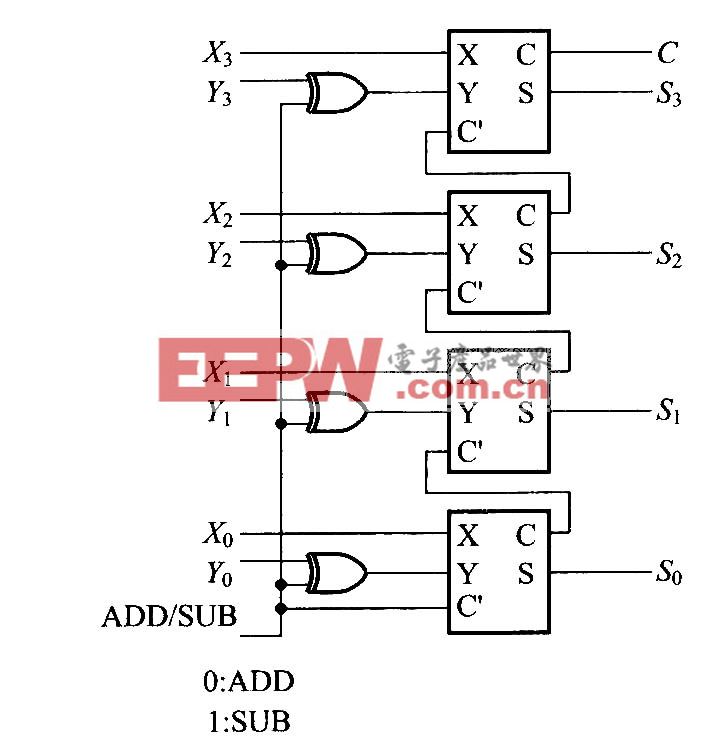

图3是一个很好的双通道运放版图。输入级非常靠近裸片中心,因此机械应力梯度最小。从一个输出级到另一个输入级的距离要大于另一种版图。从输出级到两个输入级的等温线近似等距的并行线,因此交叉耦合输入级四通道运放的抑制能力很强。这种版图的主要缺点是,输出B必须跨越两个输入级才能到达输出焊盘。从输出金属化到同相输入金属化的任何电容都将导致正反馈。这对几年前的单层金属化(SLM)工艺来说问题比较麻烦,不过通过这些运放的低增益带宽已经有所改善。这种版图具有良好的散热性能,但是,在规划同一产品系列中的四通道版本时又会遇到问题。 双通道版图还有另外一种选择,如图4。在一个产品系列中要规划四通道产品时可以采用这种版图,因为这种版图可以被复制,再经垂直翻转就能快速生成四通道版图。输入和输出相当靠近正确的封装引脚。四通道运放的标准引脚输出如图5所示。

这种版图存在几个微妙的问题:(1)输入级不在裸片中心,而裸片中心是最低的机械应力梯度点,具有最小的失调电压;(2)从输出级到输入级的距离不够远;(3)从一个输出级到另外一个输入级的热波将使等温线变成曲线,因而无法被交叉耦合的输入对完全抑制,并造成从一个通道至另一个通道的串扰。

这些问题使设计师处于两难境地:对双通道运放来说最优的版图对四通道运放而言不是最优的。每个单通道、双通道或四通道运放的单个版图可以从头开始设计,但考虑到上市时间和开发成本,标准设计过程是要尽可能多地重复利用某个设计。当某个产品系列中只需要单通道或双通道运放时,双通道的版图通常是最优的。有趣的是,将图3进行水平翻转可以得到同样的四通道版图,因此与版图设计合理的双通道或单通道运放相比,四通道运放性能指标会较差。

几年前,有个制造商做出了指标非常好的四通道运放。秘诀是使用了一个特殊的引脚框,可接受两个双裸片,即混合器件或多芯片模块(MCM)。这种产品需要在内部完成装配,或与外部装配工厂进行紧密合作。最终的良品率近似等于各个裸片良品率的乘积。例如,如果裸片良品率是99%,那么最终良品率将是0.99×0.99 = 98.01%,这是完全可以接受的。另一方面,如果裸片良品率为90%,对于规格要求很严的器件来说这是很有可能的,那么总的良品率将是0.9×0.9 = 81%。

2009年12月曾有人展开过一项研究,通过五家半导体公司的网站统计单通道、双通道和四通道产品种类的 数量。调研结果如下:

单通道: 598,占 39.7%

双通道: 556,占37%

四通道: 350,占 23.3%

这里包括了大批量应用运放、音频放大器、高速、带有或不带有关断引脚的器件(算作两种)以及单位增益稳定和非完全补偿器件,在精密应用领域,如低失调电压或低噪声,总数会向单通道和双通道倾斜

电子管相关文章:电子管原理

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理 绝对值编码器相关文章:绝对值编码器原理

评论