7段LED显示解码器

简介

本文引用地址:https://www.eepw.com.cn/article/202305/447172.htm大多数情况下,七段式显示器用于显示数字手表、计算器、时钟、测量仪器和数字计数器等的数字。一般来说,LCD和LED段提供数字和字符的显示输出。

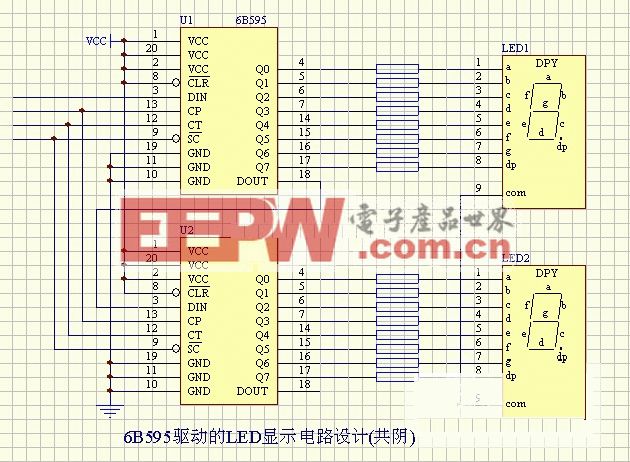

然而,为了显示字符和数字(以产生十进制读数),最常用的是七段显示器。大多数情况下,这些显示器是由数字IC的输出级驱动的(必须对输出级进行视觉指示),如锁存器和十年计数器等。

但这些输出是以4位二进制编码十进制(BCD)的形式,不适合直接驱动七段显示器。

显示解码器用于将BCD或二进制代码转换成7段代码。它一般有4条输入线和7条输出线。在这里,我们使用逻辑门设计一个简单的显示解码器电路。

尽管有商业化的BCD到7段解码器,但从经济和知识的角度来看,使用逻辑门设计一个显示解码器可能被证明是有益的。

显示器解码器电路的原理

其基本思路是利用组合逻辑电路驱动一个共阴极7段LED显示屏。 该逻辑电路设计有4个输入和7个输出,每一个都代表显示IC的一个输入。使用卡诺夫图,设计了显示器每个输入的逻辑电路。

电路背后的理论:

这个电路的首要方面是解码器。解码器是一个组合电路,用于将二进制或BCD(二进制编码的十进制)数字转换成相应的十进制数字。它可以是一个简单的二进制到十进制的解码器或BCD到7段的解码器。

另一个相关部分是组合逻辑电路。一个组合逻辑电路是一个只由输出和输入组成的逻辑门系统。组合逻辑电路的输出只取决于输入的当前状态,而不取决于其他。这类电路的最佳例子是编码器和解码器,多路复用器和去多路复用器,加法器,减法器等。

为了理解这些逻辑电路的设计和操作,人们需要对布尔代数和逻辑门有充分的了解。例如,需要遵循的几个基本布尔代数规则是互补定律、关联定律、德-摩根定律等。

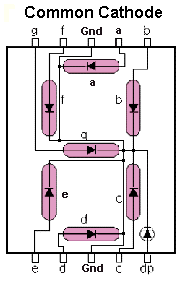

一个7段式LED显示屏由8个LED排列组成,所有的阳极是共用的,或者阴极是共用的。 一个共阴极的7段显示屏由8个引脚组成--7个输入引脚,从'a'到'g',第8个引脚为公共接地引脚。

7段显示器解码器电路设计

第1步:设计的第一步涉及到对共阴极7段显示器的分析。 7段显示器由 "H "形式的LED排列组成。 用每个小数点的输入组合构建一个真值表。例如,小数点后的数字1将命令b和c的组合(参考下面的图表)。

7段式LED

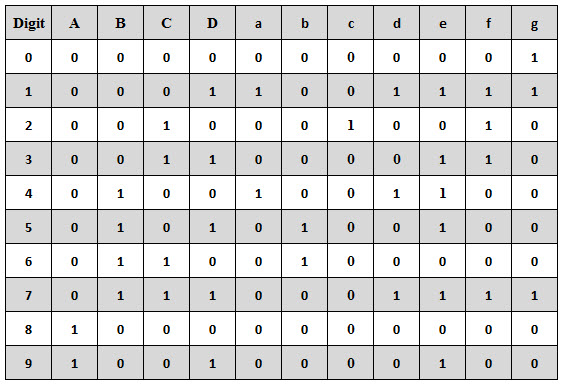

第二步:第二步是构建真值表,列出7个显示输入信号、十进制数字和相应的4位二进制数字。

解码器设计的真值表取决于7段显示器的类型。正如我们上面提到的,对于普通阴极七段显示器,解码器或段码驱动器的输出必须是高电平,以使段码发光。

下图显示了带共阴极显示的BCD转七段解码器的真值表。在真值表中,有7个不同的输出列,分别对应7个段。

假设a段的列显示了它要被点亮的不同组合。所以'a'对数字0、2、3、5、6、7、8和9是有效的。

BCD到共阳极7段真值表

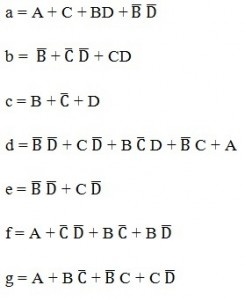

从上面的真值表来看,每个输出函数的布尔表达式可以写为

a = F1 (A, B, C, D) = ∑m (0, 2, 3, 5, 7, 8, 9)

b = F2 (A, B, C, D) = ∑m (0, 1, 2, 3, 4, 7, 8, 9)

c = F3 (A, B, C, D) = ∑m (0, 1, 3, 4, 5, 6, 7, 8, 9)

d = F4(A,B,C,D)= ∑m(0,2,3,5,6,8)

e = F5 (A, B, C, D) = ∑m (0, 2, 6, 8)

f = F6 (A, B, C, D) = ∑m (0, 4, 5, 6, 8, 9)

g = F7 (A, B, C, D) = ∑m (2, 3, 4, 5, 6, 8, 9)

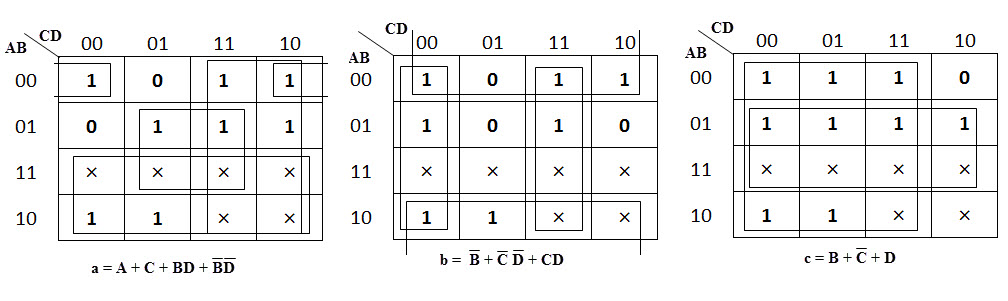

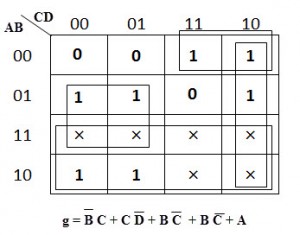

第三步:第三步是为每个输出项构建卡诺夫图,然后将其简化,得到每个输出项的输入逻辑组合。

K-Map的简化

下图显示了共阴极七段解码器的K图简化过程,以便设计组合电路。

从上面的简化中,我们得到的输出值为

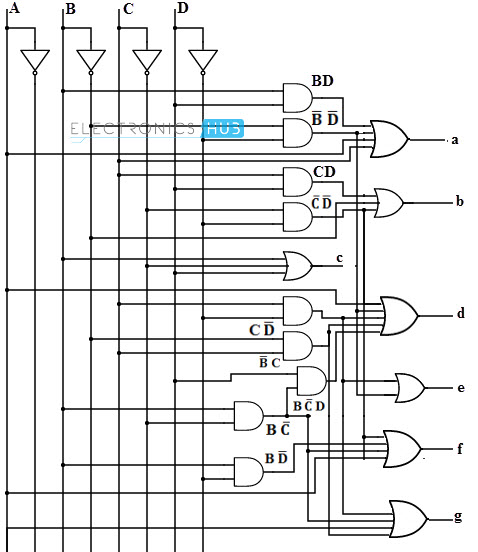

第4步:最后一步是为每个输出信号画一个组合逻辑电路。任务完成后,可以用4个输入(A,B,C,D)和7段显示(A,B,C,D,E,F,G)作为输出,画出一个组合逻辑电路。

显示解码器的电路操作

电路的操作可以通过真值表本身来理解。当所有的输入都连接到低逻辑时,组合逻辑电路的输出将驱动所有的输出LEDs,除了'g'。 因此,数字0将被显示出来。类似的操作将发生在所有其他输入开关的组合上。

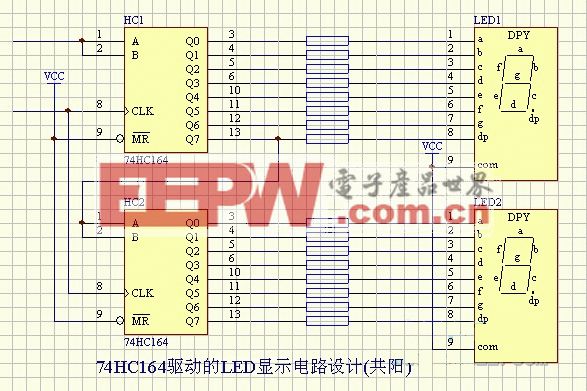

实际上,BCD转7段解码器是以集成电路的形式出现的,如74LS47。 除了常规的4个输入引脚和7个输出引脚外,它还包括一个用于分段测试的点亮测试引脚、用于在多个显示系统中清零的纹波消隐输入引脚、用于级联的纹波消隐输出引脚和一个消隐输入引脚。

显示解码器电路的应用

这个电路可以使用定时器和计数器进行修改,以显示时钟脉冲的数量。

这个电路可以被修改为开发一个字母显示系统,而不是一个十进制数字显示系统。

它可以作为一个定时器电路使用。

显示解码器电路的局限性

这个电路涉及很多逻辑门,而且相当复杂。

每个逻辑门的定时延迟是一个值得关注的问题,而且这个电路在用于显示脉冲数时可能不会产生准确的结果。

这是一个理论上的电路,可能需要进行一些修改。

评论