基于USB总线的ADSP-TS101S链路口加载

图4 中的FIFO负责对输出数据进行缓冲,当输入数据的速率高于Link Port时钟的频率时,Link Port的数据可以先存在FIFO数据中,当存入一定数量以后,再以Link Port的时钟把数据读出。当输入数据的速率低于Link Port的时钟数率的时候,Link Port的数据同样可以先存在FIFO中,当存入整数倍的4字数据量后,再以Link Port的时钟的数率发送出去。

图4中的控制模块是Link Port发送模块的关键模块,主要负责产生读FIFO的读使能信号和Link Port的发送时钟根据Link Port发送的时序特点,使用状态机来实现数据流的控制。当Link Port没有工作时,保持等待状态。需要传输数据时,首先检查LxCLKIN是否为高电平,若是,则说明接收端为接收模式并且接收缓冲器为空,可以初始化一次发送,否则要等待。开始传输数据时,数据首先被写入FIFO中,当判断

到FIFO的输出信号EMPTY为高时,将处于默认高电平的LxCLKOUT信号拉低,在经过6个时钟周期的低电平后(在此期间检测LxCLKIN是否一直为高电平),LxCLKOUT拉高形成第一个LINK时钟上升沿,这个时候应该在数据线上产生FIFO内的第一个输出数据。LxCLKOUT下一周期拉低,第2个数据输出,这样经过16个时钟周期以后表示一次4字传输完毕。然后检测FIFO中剩余的数据FIFO_RDATA_COUNT,若大于4则继续上面的传输操作,否则,说明FIFO中只剩最后一个4字,这次传输LxCLKOUT的最后一个时钟上升沿产生以后,不再变低,一直保持高电平。然后,把本模块中的所有临时寄存器和FIFO复位。在产生完足够长度脉冲长度的清零信号后状态机重新进入等待状态。

3.2 USB接口模块

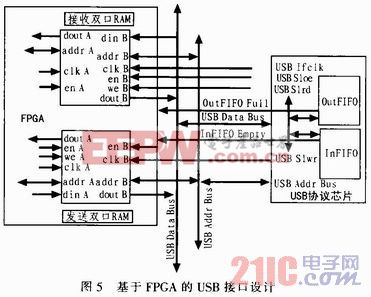

USB接口模块采用FPGA控制USB协议解析芯片来实现。其实现框图如图5所示。本文引用地址:http://www.eepw.com.cn/article/202238.htm

本方案中,USB2.0协议解析芯片选用CYPRESS公司的CY7C68013A,它将一个USB外设所需的所有功能集成在一块芯片上。芯片提供了3种传输数据的方式,文中选择从FIFO(SlaveFIFO)模式。在SlaveFIFO模式下,8051微控制器不在数据的传输通路上,只负责设备的初始化和相应主机的控制传输请求,高速大批量的数据传输通过外部的主控者通过SlaveFIFO接口直接将数据填充到FX2LP的端点中(或者从里面读出),然后由硬件控制将数据传输给主机。

Slave FIFO的读写方式有两种:同步读写以IFCLK为时钟,IFCLK可以外部输入,也可以使用内部的30 MHz或者48 MHz时钟;异步读写时IFCLK信号无效,只需要提供读写信号即可进行数据读写。本文选择同步读写。

FPGA采用Xilinx公司的XC3S1000。FPGA在其内部建立2个双口RAM,来缓存收发数据;并与协议解析芯片的各控制信号相连,实现对其的读写控制。文中仅使用这个芯片的接收逻辑实现加载文件的USB总线传输,发送逻辑只用来做辅助调试和状态监测。

评论