PCI Express协议实现与验证

摘要:称为第3代I/O接口技术的PCI Express总线规范的出现,从结构上解决了带宽不足的问题,有着极为广阔的发展前景。基于Verilog HDL硬件描述语言及可综合化设计理念,完成了PCI Express IP核RTL代码的设计。IP核代码使用Verilog HDL语言编写,分模块、分层次地设计了事务层、数据链路层和物理层的逻辑子层,并进行了可综合化设计与代码风格检查。对设计的PCI Express IP核的功能分别从协议层次和应用层次进行了验证。具体实现上,采用Denali公司的PureSuite测试套件对IP核的协议兼容性进行验证,验证范围覆盖了IP核的3个层次以及配置空间,采用QuestaSim仿真工具对IP核的应用层进行验证。仿真结果表明,设计的PCI Express IP核工作正常,性能优良。

关键词:PCI Express协议;IP核;验证;I/O接口

0 引言

当下,计算机系统使用的主流内部总线技术为PCI总线。随着千兆以太网、RAID阵列等高带宽设备的出现,PCI总线133 MB/s的带宽已明显不能满足应用的需要。根据PCI总线的性能不足及计算机系统的应用需求,第3代I/O总线接口技术PCI Express应运而生。PCI Express是一种应用于各种计算与通信平台的高带宽、点对点串行互联协议,支持虚通道、流量控制机制及热插拨,具有错误处理及错误报告功能,并在软件上与PCI兼容,具有鲜明的技术优势和广阔的应用前景。基于将PCI Express理论优势转化为实际应用优势的考虑,设计了PCI Express IP核,并进行了可综合化设计与代码风格检查,最后对设计的PCI Express IP核分别从协议层次和应用层次进行了较为充分的功能验证。

1 PCI Express协议

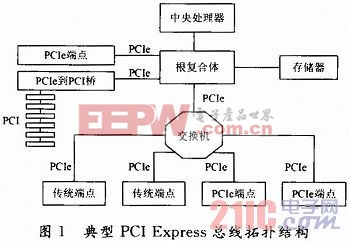

较之PCI总线,PCI Express在总线技术与结构上实现了较大飞跃,提供了高速、高性能、点到点、双单工、串行、差分信号链路来互联设备。PCI Express的基本结构包括根复合体(Root Complex)、交换机(Switch)以及端点设备(Endpoint)等,本文设计的PCI Expresb;IP(Intellectual Property)核属于PCI Express端点设备。PCI ExpreSS总线典型拓扑结构如图1所示。

根复合体(RC)为下层I/O设备连接到CPU和主存储器系统提供了路径,一个根复合体可支持一个或多个PCI Express端口;端点设备(EP)是PCI Express事务的请求发起者(Requester)或应答者(Compieter),端点设备又分为传统端点、PCI Express端点和根复合体集成端点;交换机(Switch)是由多个虚拟PCI-to-PCI桥设备组成的,其主要功能是为上游器件和下游器件的通信选择路径。

评论