掌控人工智能的力量:使用莱迪思sensAI快速上手

在莱迪思FPGA中构建推理引擎

本文引用地址:http://www.eepw.com.cn/article/201902/397747.htm设计AI推理模型的硬件需要不断平衡所需资源数量与性能和功率要求。莱迪思的ECP5和UltraPlus产品系列能轻松实现这种平衡。

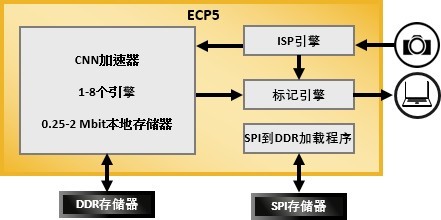

ECP5系列拥有三种不同规格的器件,能够运行一到八个推理引擎。它们集成的本地存储器从1 Mb到3.7 Mb不等。功耗最高仅为1 W,尺寸也只有100 mm2。

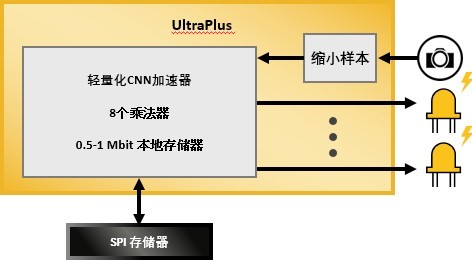

相比之下,UltraPlus系列的功耗水平低至ECP5系列的千分之一,仅为1 mW。占用的电路板面积仅为5.5mm2,包括了最多8个乘法器和最多1 Mb的本地存储器。

莱迪思还提供可在这些器件上高效运行的CNN IP以及可用于ECP5系列的CNN加速器。

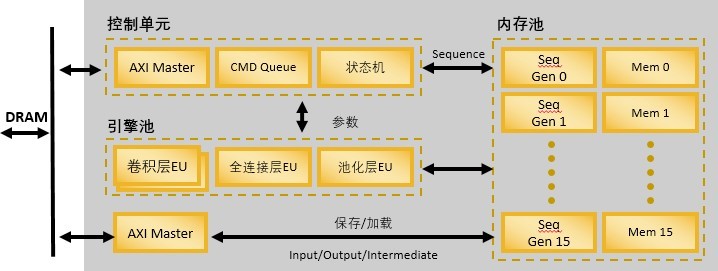

图4 适用于ECP5系列的CNN加速器

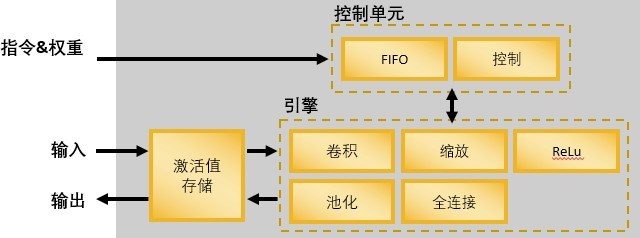

莱迪思还提供可用于UltraPlus系列的轻量化CNN加速器。

图5 适用于UltraPlus系列的轻量化CNN加速器

这里暂且不谈细节;重点在于您无须从头开始设计自己的AI引擎。您可以联系莱迪思获取关于这些IP的更多信息。

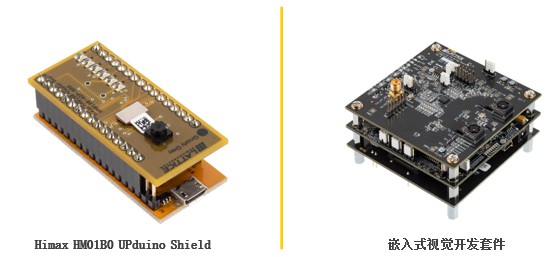

最后,您还可以在开发模块上运行并测试这些演示,两个模块分别对应这两种产品系列。Himax HM01B0 UPduino Shield采用了一片UltraPlus FPGA, 尺寸为22x50 mm2。嵌入式视觉开发套件采用了一片ECP5 FPGA,尺寸为80x80 mm2。

Himax HM01B0 UPduino Shield 嵌入式视觉开发套件

图6 评估AI应用的开发模块

有了FPGA、软IP和其他处理数据所需的硬件部分,就可以使用Lattice Diamond设计工具进行编译,从而生成位流,在每次上电后对目标设备中的FPGA进行配置。

在莱迪思FPGA上构建推理模型

创建推理模型与创建底层运行平台大不相同。它更抽象,涉及更多运算,且不涉及RTL设计。这一过程主要有两个步骤:创建抽象模型,然后根据所选平台优化模型的实现。

模型训练在专门为此过程设计的框架中进行。最流行的两个框架是Caffe和TensorFlow,但不限于此。

CNN由很多层构成——卷积层,可能还会有池化层和全连接层——每一层都有由前一层的结果馈送的节点。每个结果都在每个节点处加权重,权重多少则由训练过程决定。

训练框架输出的权重通常是浮点数。这是权重最为精确的体现,然而大多数网络边缘设备不具备浮点运算功能。这时我们需要针对特定平台对这个抽象模型进行优化,这项工作由莱迪思的神经网络编译器负责。

编译器可以实现加载和查看从某个CNN框架下载的原始模型。您可以运行性能分析,这对模型优化最关键的方面——量化至关重要。

由于无法处理浮点数,因此需要将它们转换为整数。对浮点数四舍五入也就意味着精度会降低。问题是, 什么样的整数精度才能满足您想要的精度?通常使用的最高精度为16位,但是权重和输入可以表示为较小的整数。莱迪思目前支持16、8和1位的设计实现。

1位的设计实际是在一位整数域中进行训练以保持精度。显然,更小的数据单元意味着性能更高、硬件尺寸更小以及功耗更低。但是,精度太低就无法准确地推断视野中的物体。

图7 可以对单个模型进行优化以适用于不同的设备

神经网络编译器能让您创建代表模型的指令流,然后可以模拟或直接测试这些指令,从而判断在性能、功耗和精度之间是否达到了适度的平衡。测试的标准通常是看一组测试图像(与训练图像不同)中正确处理的图像的百分比。

通常可以通过优化模型来优化运行,包括去掉一些节点以减少资源消耗,然后重新训练模型。这一设计环节可以微调精度,同时保证能在有限的资源下顺利运行。

两个检测实例

在以下两个不同的视觉案例中,我们将看到权衡是如何发挥作用的。第一个应用是人脸检测;第二个是人员侦测。我们将看到不同FPGA之间存在的资源差异如何影响到相对应的应用的性能和功耗。

两个示例的输入都源自同一个摄像头,两者都在相同的底层引擎架构中运行。在UltraPlus设计实例中,图像的尺寸缩小后通过8个乘法器进行处理,利用了内部存储器并使用了LED指示灯。

图8 UltraPlus平台用于人脸检测和人员侦测应用

ECP5系列资源更多,提供了一个计算能力更强的平台。摄像头捕捉的图像在发送到CNN之前在图像信号处理器(ISP)中进行预处理。处理结果与原始图像在标记引擎上比对,从而将文本或注释覆盖在原始图像上。

图9 ECP5平台用于人脸检测和人员侦测应用

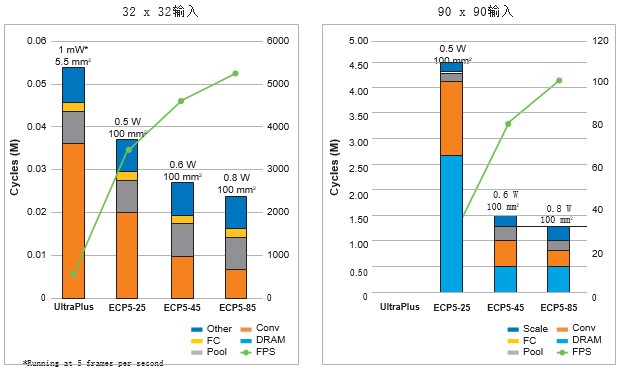

我们可以使用一系列图表来衡量两种应用的性能、功耗和占用面积情况。对于每个应用,我们做了两组示例:一组输入较少,一组输入较多。

图7表示了人脸检测应用的结果。两组分别采用了32x32输入和90x90输入的情况。

图10 在UltraPlus和ECP5 FPGA上实现简单和复杂的人脸检测应用时的性能、功耗和占用面积

左侧的轴代表处理一张图片需要的周期数量以及这些周期的分配情况。右侧的轴代表在各器件(绿线)上实现的每秒帧数(fps)。最后,每种情况下还标注了功耗和占用面积。

左侧的32x32输入示例中,橙色部分代表卷积层上运行的周期。在四个示例中,UltraPlus的乘法器数量最少;其他三片ECP5 FPGA的乘法器数量依次递增。随着乘法器数量的增加,卷积层所需的周期数减少。

90x90输入的示例位于右侧,得到的结果完全不同。在每个柱形图的底部有大面积的蓝色区域。这是由于设计更为复杂,使用了除器件内部存储空间以外的更多存储器。由于需要占用外部DRAM,性能就有所损失。需要注意的是,这种设计无法使用较小的UltraPlus器件。

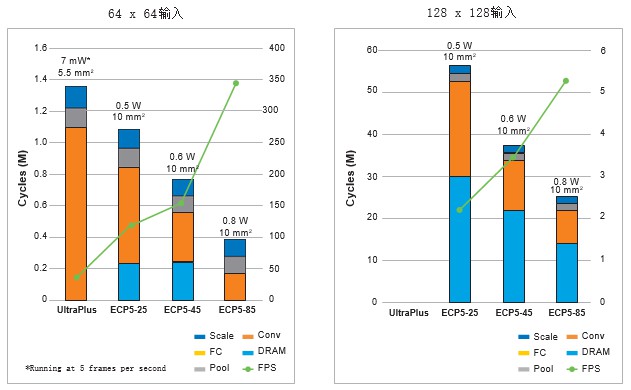

人员侦测应用的情况类似。两组分别采用了64x64输入和128x128输入的情况。

图11 在UltraPlus和ECP5 FPGA上实现简单和复杂的人脸检测应用时的性能、功耗和占用面积

同样,较多的乘法器会减少卷积层的负担,而依赖DRAM则会影响性能。

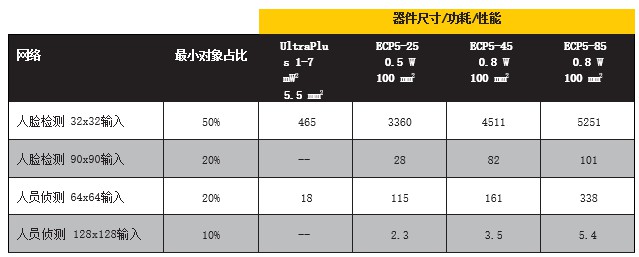

图9总结了各类情形下的性能。它包括了对图像中最小可识别对象或特征的度量,用视野范围的百分比表示。在这里使用更多输入能够为较小的目标提供更多分辨率。

图12 两个应用示例在四片FPGA上的性能总结

小结

总之,使用莱迪思sensAI产品提供的资源,您就可以在莱迪思FPGA上轻松实现要求低功耗、具有灵活性和可扩展性的网络边缘AI推理设计。它可以提供成功部署AI算法所需的关键要素:

• 神经网络编译器

• 神经引擎软IP

• Diamond设计软件

• 开发板

• 参考设计

评论