基于PLL 和DDS 的跳频信号发生器设计

0 引言

本文引用地址:https://www.eepw.com.cn/article/201808/387309.htm跳频信号源主要由两部分组成:控制部分和频率合成部分。频率合成部分是跳频信号源的主要组成部分,频率合成是利用一个或多个高稳定晶体振荡器产生出一系列等间隔的离散频率信号的一种技术,早期的通信系统都是采用调谐(机械和电子)的方法实现特定频道上的通信或者从一个频道转换到另一频道,这种方法严重地限制了通信质量的提高。采用频率合成器后,可以用数字预置的方法提供大量精确且能迅速转换的载波信号和本振信号,从而大大地提高了通信质量,而且许多新的通信体制也就有可能得到实现。控制部分是人机接口,频率合成器在控制部分作用下产生所需的频率。

当前DDS(直接数字合成器)与 PLL(锁相频率合成器)混合的技术方案主要有:频偏由DDS产生的PLL 合成器和参考源由DDS 提供的PLL合成器两种,其中电路结构较简单且应用较多的是参考源由DDS 提供的PLL频率合成器。本设计方案采用以AD9850作参考信号源的PLL 频率合成器。

1 DDS+PLL 方案工作原理

由于PLL 合成器的参考基准是由DDS 提供的,它可以做到以10-3 Hz 或10-6 Hz变化,因而整个频率合成器的输出频率间隔可以做得较小;该研究与设计合成器的输出频率精度和频率切换时间均由DDS决定。由于DDS 频率切换时间可达到ns级,频率和相位精度很容易达到10-3 Hz 级,因此系统性能得到显著改善。

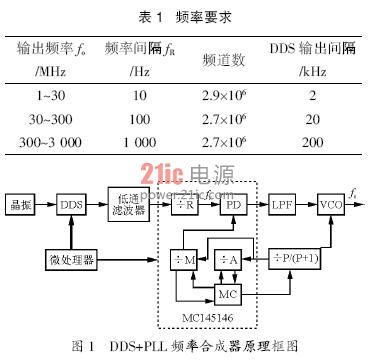

本方案中PLL部分采用大规模集成电路频率合成器MC145146,工作频率及间隔如表1 所列,原理框图如图1所示。

将高稳定度晶振产生的10 MHz 标准频率作为DDS 的时钟信号,由DDS 产生所需频率,经MC145146 的R 分频器除200,得到参考频率fR,加到鉴相器PD 上。压控振荡器VCO 输出频率fo经前置分频器除[P/(P+1)],计数器A 和主计数器M 分频后,送入鉴相器PD 中与fR进行比相,并使PD输出误差电压。误差电压经低通滤波器LPF平滑后加到压控振荡器VCO上,使VCO锁定。

MC145146是双模频率合成器电路,其内部吞除计数器A和外部前置计数器P/(P+1)配合,可实现脉冲吞除计数,从而使合成器的输出频率扩展到 VHF波段。脉冲吞除计数方法简述如下:计数开始时,模控制信号MC 为低电平,前置分频器按P+1 模式工作,A 和M同时计数。当A 计数计满后,A 停止计数,控制逻辑使模控制信号MC 变为高电平,前置分频器按P模式工作。M计数器继续计数,直至M 计数器计满,便输出一个分频脉冲至鉴相器PD。至此,一个计数周期结束。在输出一个分频脉冲同时,控制逻辑使计数器M 和A 重新装入分频数,模控制信号重新回到低电平,前置分频器重新回到P+1 模式,以便进入下一个计数循环。这样总的分频数N为

2 硬件设计

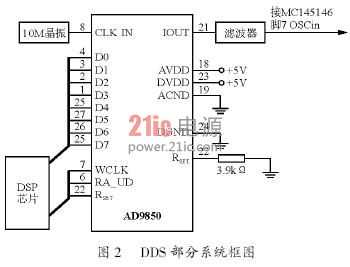

2.1 DDS 部分

DDS 部分[1]系统框图如图2 所示,滤波器采用2~20 kHz 自调谐带通滤波器,当输入频率在宽带范围内变化时,由于这个宽带范围随不同种类的换能器而不同,所以为了得到最佳噪声抑制要自动调节滤波器的中心频率。不要求有参考频率、内部振荡器及同步电路,调节电容器可把频率范围按10 进制扩展。当滤波器与输入频率未调谐时,相移不是180毅,相位检测器给FET 的栅极提供误差信号以控制其漏-源电阻。鉴相器和FET 构成滤波器的负反馈环路,相位误差可以改变FET 的电阻,从而重新调谐滤波器到新的中心频率。

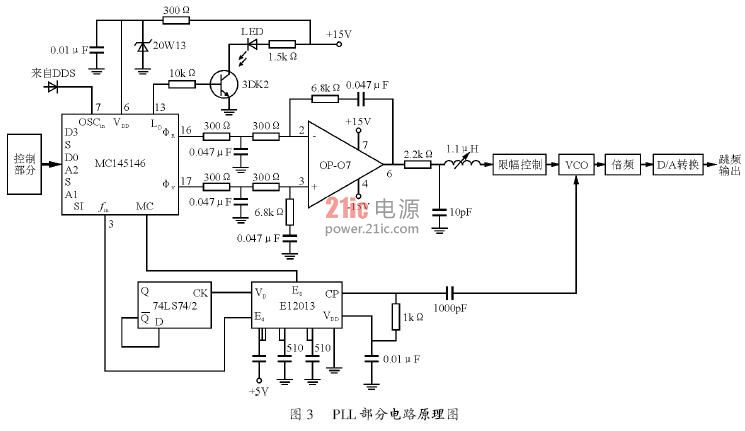

2.2 PLL部分

PLL部分[2]电路原理图如图3所示,图中E12013和74LS74/2 组成双模前置分频器[衣(20/21)]。环路滤波器采用OP-07 构成的有源比例积分滤波器。该滤波器具有滞后超前网络,其比例特性可以加快环路捕捉速度,其相位超前特性可以增大环路的相位稳定余量,同时提供鉴相输出电平与VCO相匹配的增益。

压控振荡器是由定时器NE555、运放LM301D 以及无源元件构成的简单而精密的电压-频率变换器,其工作过程为:输入电压经积分后变换成正向斜波输出,当斜波电压达到2/3E 时定时器NE555 被触发,脚3 和脚7 输出低电平。

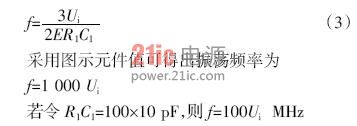

这时Q1导通,电容C1 迅速放电,而C3按时间常数R5C3 放电。当定时器的脚2 到达1/3E 时,定时器复位,脚3、7 输出为高电平。这时Q1 截止,开始下一个周期。此变换器的回扫时间即放电时间大约为1 滋s,若回扫时间和工作周期相比可以忽略,则频率与电压的关系为

限幅电路控制LPF 的输出电压,倍频电路控制VCO 的输出频率以保证所需,对应关系如表2所列。

D/A转换部分将数字信号变换成模拟信号。

3 结语

本跳频频率合成器由于数字分频器及鉴相器均集成在芯片内,外接电路有滤波器,VCO,有源低通滤波器及高速双模分频器E12013、74LS74,因此整个合成器体积小,外接电路少、调试方便,另外由于DDS 中应用了AD9850,使得系统的精度较高。

评论