一种基于每周期两位转换的流水线逐次逼近ADC

作者 何沁 电子科技大学 微电子与固体电子学院(四川 成都 610054)

本文引用地址:https://www.eepw.com.cn/article/201806/382304.htm何沁(1993-),女,硕士,研究方向:SOC/SIP系统芯片技术。

摘要:随着半导体制造工艺的革新与芯片供电电压的下降,高性能的模数转换器设计面临新的挑战。传统的逐次逼近SAR模数转换器与流水线Pipelined模数转化器难以实现高转化速率、高精度与低功耗的性能指标,常常需要牺牲某个指标来满足其他要求。针对传统模数转换器电路结构在精度、转换速率以及功耗方面的不足之处,提出了一种基于每周期两位转化的流水线逐次逼近12位5兆的ADC,采用两级流水线结构,第二级采用每周期两位量化的SAR模数转换器实现,可以充分利用输入电压幅值较小的特点,实现整体电路性能的优化,最终可在5兆的采样速度下达到前仿11.63位的有效位数。

0 引言

近年来,计算机、通信和多媒体技术飞速发展,全球高新领域的数字化程度不断加深,在许多电子系统中都需要用到模数转换器来将电压、电流等模拟信号转化为数字编码后再进行处理,以利用大规模数字集成电路强大的数据处理能力。

随着半导体制造工艺的革新与芯片供电电压的下降,高性能的模数转换器设计面临新的挑战。文献[1]中表明传统的逐次逼近SAR模数转换器与流水线Pipelined模数转化器难以实现高转化速率、高精度和低功耗的性能指标,常常需要牺牲某个指标来满足其他要求。

传统的SAR模数转换器由比较器、数模转化器和数字控制逻辑组成[2]。数字控制逻辑根据比较器的输出结果依次决定输出编码每一位的值。利用逐次逼近的二分算法方式每次转化都需要N个量化周期,经历N次比较,其转换速率受到了很大的限制[3]。除此之外,传统的SAR模数转换器只利用了比较器输出的电压比较结果而忽略了比较器可以提供的其他信息,使得每次量化只能单位进行,这也严重限制了SAR模数转换器的转换速率[4]。

传统的流水线Pipelined模数转化器属于多级转换器[5],每一级都有采样保持电路,并有一个级间放大器对本级的量化余量进行放大,再输出给后级作进一步的量化。采样保持电路使得在一个周期内只需每个流水线级分别完成量化与残差放大,而无需整个转换器一次性完成转化,因此转换速率不会随着级数的增加而下降,但由于需要用到增益精确的级间放大器,整体功耗较大,特别是在低压短沟道的先进工艺下,实现高增益的运算放大器用以设计增益稳定的反馈网络显得更加困难[6]。

针对传统模数转换器电路结构在精度、转换速率以及功耗方面的不足之处,本文提出了一种基于电压域与时域结合量化的流水线逐次逼近的12位5兆的ADC,采用两级流水线结构,第二级采用电压域与时域结合量化的SAR模数转换器实现,可以充分利用输入电压幅值较小的特点,实现整体电路性能的优化。

1 原理分析

为了实现ADC电路的整体性能提高,采用的基于电压域与时域结合量化的流水线逐次逼近ADC包括第一级ADC、第二级ADC和级间单位增益缓冲器。

1.1 系统架构

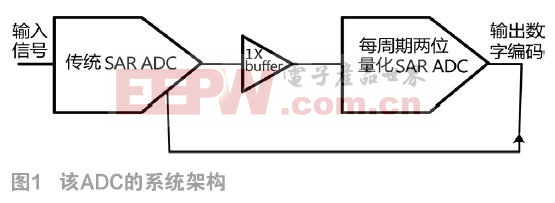

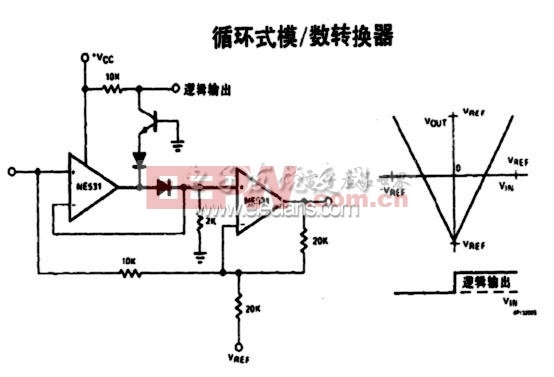

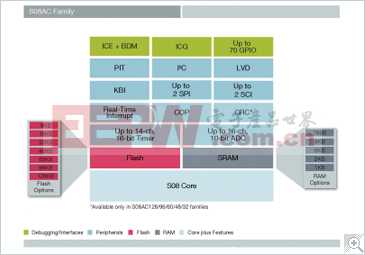

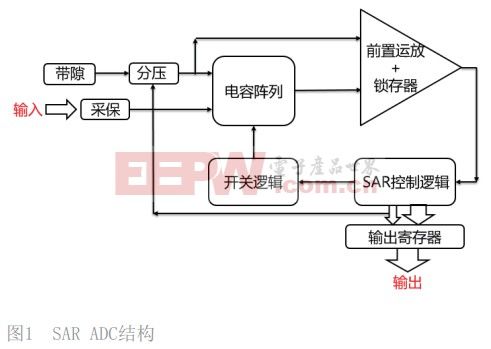

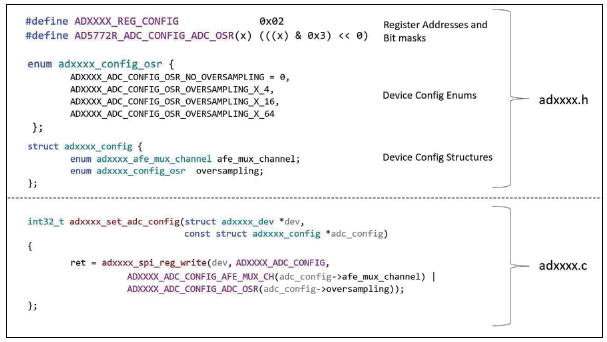

相较于传统结构,提出了一种具有创新性的整体系统架构,如图1所示,包括第一级传统SAR ADC,第二级电压域与时域结合量化SAR ADC和单位增益缓冲器,第一级SAR ADC的输入端连接输入信号,其第一级输出端输出ADC的高位量化结果,第二级输出端输出ADC 的低位量化结果,第一级量化结果和第二级量化结果作为最终输出码字依次编码后得到最终量化结果。

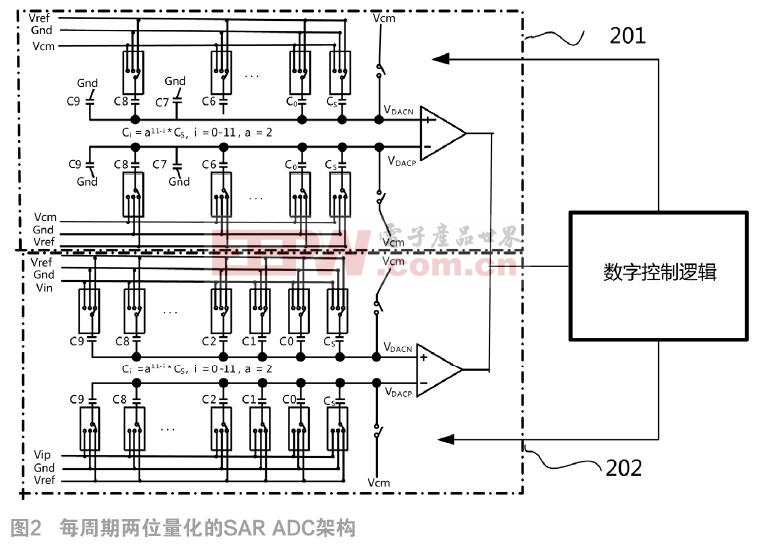

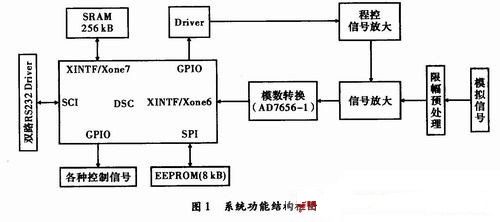

第二级每周期两位量化的SAR ADC如图2所示,包括时域基准的模数转换器、电压域基准的模数转换器和数字逻辑控制模块。时域基准的模数转换器(图2中201)包括第一比较器和N位的第一电容阵列,第一电容阵列上极板分别连接第一比较器的正负输入端,电容下极板通过开关连接地电位、共模电位或基准电位。电压域基准的模数转换器(图2中202)包括第二比较器和N位的第二电容阵列,第二电容阵列上极板分别连接第二比较器的正负输入端,电容下极板通过开关连接地电位、第二级ADC的输入信号或基准电压。数字逻辑控制模块的输入连接第一比较器和第二比较器的输出端,其输出作为第二级ADC的量化结果输出。

1.2 量化过程分析

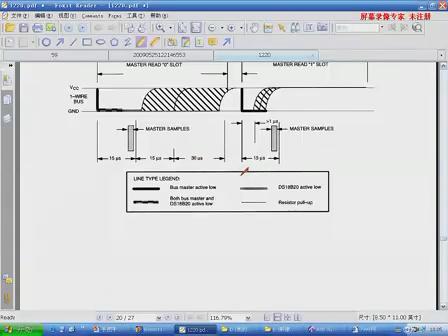

如图3所示的时序图,本论文叙述的ADC通过两级流水线的方式实现量化,每一级ADC为逐次逼近模数转换器。第一级ADC按照传统SAR的工作方式进行逐次逼近,每个周期量化1位,经历采样、量化和缓冲保持的过程。第二级ADC利用电压域与时域相结合的方式实现每个周期量化2位,提高了电路转换的速率。第一级ADC和第二级ADC通过流水线的工作方式实现了在同时间内的量化,提高了整体的转换速率,本文中采用两级SAR而不是整体流水线的实现方式,考虑到SAR模数转化器的低功耗特性,这也会降低整个电路的功耗。输入信号经过第一级量化,信号的幅度在逐次逼近中不断减小。与此相对应的比较器的输出延时随着比较器输入电压幅值的减小而呈指数增大,而比较时间随幅值的变化差异越大,比较的精度也越高。利用这样一个特性,不需将第一级量化后的残差电压进行放大,只需级联一个单位增益缓冲器将第一级的输出电压传递到第二级作为输入电压即可,这进一步降低了整体电路功耗以及提高了线性度。

本文中第一级ADC采用4位有效位数的模塑转换器,而第二级ADC采用8位精度的模数转换器来实现5兆的转换率。值得说明的是,第二级ADC中电压域基准模数转换器的连接方式与传统SAR模数转换器的连接方式一致,而时域基准模数转换器的最高位电容下极板始终接地电位,相应的第三位、第五位、第七位电容下极板也始终接地电位,除此之外的其他电容下极板会通过开关分别连接基准电压、地电位和共模电位,这个数模转换器的作用是在量化过程中顺序地提供1/4VREF、1/16VREF、1/32VREF、1/64VREF的电压幅值。以第一次量化来具体说明,如图4所示,第一比较器的每一位输出结果包含两位信息,一位是输入电压与参考电压的比较结果,另外一位是与输入电压大小相关的输出延时时间1。当增加一个相同的第二比较器,输入电压差为每个周期的参考电压的1/4时,第二比较器的输出时间延时0就是每个比较周期的基准时间。将该时间与第一比较器的延时时间1做比较可以判断第一比较器的输入电压压差与1/4VREF的大小关系,从而将每次量化分为4个区间,完成两位的量化。

2 仿真验证

通过对该ADC进行仿真,基于TSMC 65 nm工艺,通过Cadence软件验证。

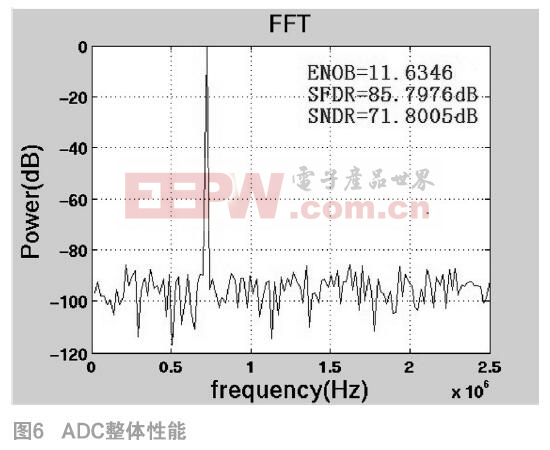

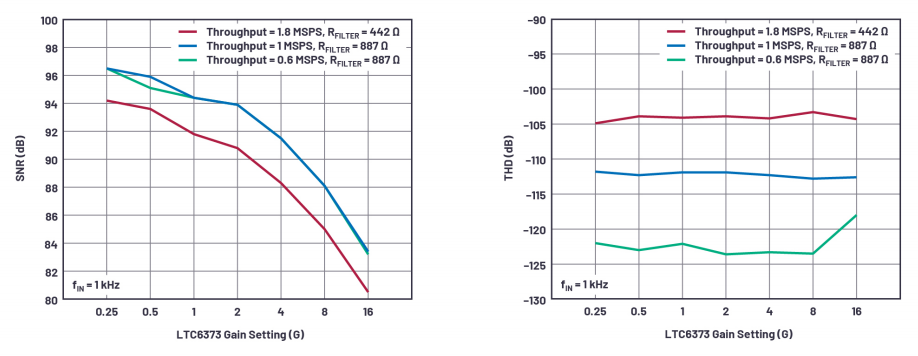

图5为输入正弦信号时电路的输出结果。可以看出,输出的量化结果呈现为阶梯状的正弦信号,与输入信号的周期性大致相同。对输出结果进行采样取点再做FFT分析可得到如图6所示的ADC整体性能,有效位数ENOB可达到11.63位,无杂散动态范围SFDR可达到85.8 dB,信号噪声失真比SNDR为72.8 dB。

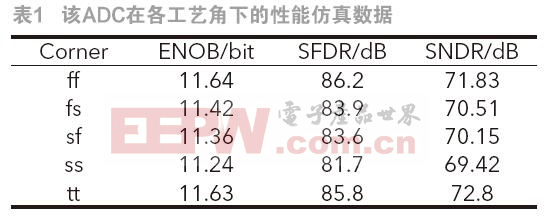

表1为各个工艺角下电路的相关数据。由表中数据可见,ADC的有效位数在各个工艺角下都可以达到11位以上,最差的ss角下也为11.24位。

由仿真验证可知,在各个工艺角下该ADC电路正常工作,可在5兆的采样速度下实现模数转换功能并且达到高于11位的有效位数。

3 结论

在TSMC工艺下,实现了一种基于电压域与时域结合量化的流水线逐次逼近12位5兆的ADC的设计。由电路的仿真验证结果可知,电路功能正常,符合设计目标。该电路的在tt工艺角下可达到11.63位的有效位数。该电路采用TSMC工艺,可集成于芯片内部,实现模拟信号对数字信号的转换。

参考文献:

[1]Z. Cao, et al., “A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 μm CMOS,” IEEE J. Solid-State Circuits, vol. 44, no. 3, pp. 862–873, Mar. 2009.

[2]H.Hong, et al., “26.7 A 2.6b/cycle-Architecture-Based 10b 1.7GS/s 15.4mW 4x-Time-Interleaved SAR ADC with a Multistep HardwareRetirement Technique,” IEEE ISSCC Digest of Technical Papers, pp. 470–472, Feb. 2015.

[3]L. Kull et al., “A 3.1 mW 8b 1.2 GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32 nm digital SOI CMOS,” IEEE J. Solid-State Circuits, vol. 48, no. 12, pp. 3049–3058,Dec. 2013.

[4]F.Ren,D. Markovic, “A configurable 12-to-237 KS/s 12.8 mW sparseapproximation engine for mobile ExG data aggregation,” in Proc. IEEE ISSCC, 2016, pp. 68–78.

[5]M.Trakimas, R. D. Angelo, S. Aeron, T. Hancock, and S. Sonkusale, “A compressed sensing analog-to-information converter with edge-triggered SAR ADC core,” IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 5,pp. 1135–1148, May 2013.

[6]M. Saberi and R. Lotfi, “Segmented Architecture for Successive Approximation Analog-to-Digital Converters,” Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol. 22, no. 3, pp. 593–606,March 2014.

本文来源于《电子产品世界》2018年第7期第55页,欢迎您写论文时引用,并注明出处。

评论