新一代的系统设计,让封装和PCB设计更简单

大多数情况下,现代电子系统设计包括设计各种元器件或者彼此隔离度较近的系统。IC 的设计和管脚输出是由芯片上的电路位置决定的。封装设计师采用“扔过墙”的芯片设计,并尽可能设计较短的封装键合线,从而使封装尽可能小。然后 PCB 设计师,通常一直怨声载道,拿起封装 IC,绞尽脑汁找出布线信号的方法,而这看上去总像是错放在某个管脚或焊球上。

本文引用地址:https://www.eepw.com.cn/article/201710/366594.htm随着如今 SoC 复杂程度的不断增加,以及多芯片封装的发展,各公司已开始认识到 IC、封装基底和 PCB 设计组之间交叉领域协作的价值。由于高管脚数目器件具有成本敏感性这一特点,工程师不得不重新考虑在对复杂的 IC 封装变量进行折衷的同时,如何规划和优化芯片的 I/O 布局。并且针对多个板级平台进行所有这些工作。现在,各种工具的出现让封装和 PCB 的设计成为一个合作、相互受益的过程。

认知设计

要最大程度地发挥作用,EDA 工具应当清楚知道会在其他过程中用到的工具。在封装和PCB 设计领域,相互之间的认识很少。诚然,FPGA 管脚输出可以在一定范围内由用户定义,但“标准”元件一般没有这样的选项。

让工具清楚设计及产品设计到工艺流程中的其他环节,这些工具就能在更短的时间内合作并交付出更好的系统设计。此外,标准 IC 芯片能以不同方式封装,这取决于终端产品的外形参数,从而为各种方式实现更为优化的解决方案。

工具之间如何快速地进行相互认知,然后合作交付出更优的设计呢?使用相同 CPU 芯片的智能手机和平板电脑的设计便可以完美地说明这一模式。显然,许多移动设备公司正在进行这样的尝试。

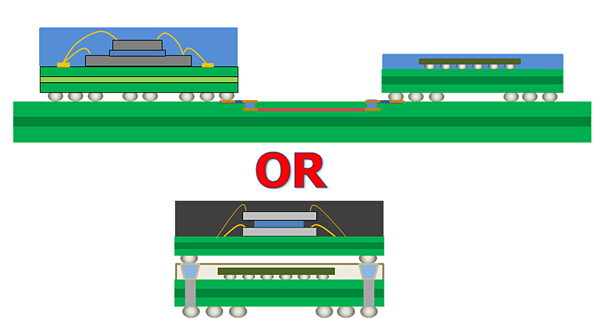

然而,相比智能手机,平板电脑的PCB基板上可用面积显然更大,其约束也更少。因此,平板电脑上的 CPU 封装可能更大,有不同的管脚输出,或者可能比智能手机上的 CPU 功耗更大功率。因此,单个“标准”封装可能并非最佳应用封装(图 1)。

图 1:平板电脑设计可能有更多可用的基板面积布局 CPU 和胶接电路,使上层封装进行运作。但对于使用相同 CPU 的智能手机而言,这种方式空间要求过大,因此更好的解决方案是使用下层封装。

现在,使用新工具,设计师能配置芯片,从封装的视角“看看”设计,再转移到 PCB(传统方法),或先了解 PCB 设计要求,再返回到封装设计中。而且,他们能拿到每个使用该 CPU 的产品,再从 PCB 回过头来设计专门为此进行设计优化的最佳封装。

从封装观点来看,物理设计规则由 PCB 设计要求决定。然后,工具与规则和封装设计师交互合作,交付出适用于该芯片特定应用的最佳封装。这种相对较快的封装设计方法还能探索不同的创意,以快速找到最佳方案。

真实案例

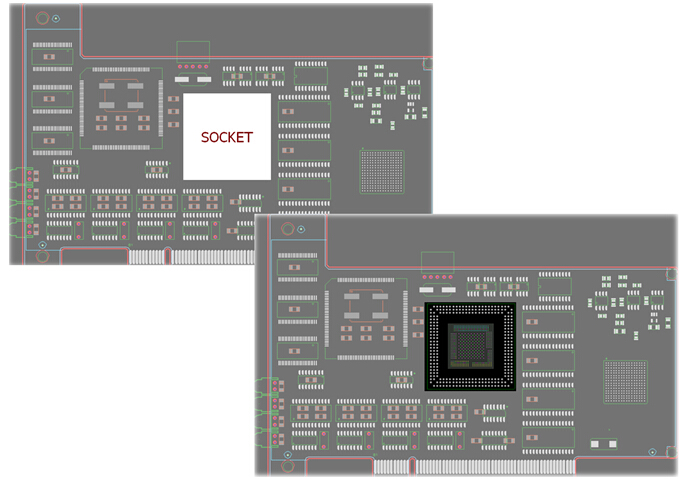

图 2 为假定的产品设计。在这个例子中,最终产品的外形参数已知,元器件也已进行初步布局。注意顶部的说明,已预留布局 CPU 的位置。使用这种输入,工具可以开始路径查找,即基于 PCB 设计师和封装设计师编写的规则,尝试多种封装配置。

图 2:通常,物理外形参数是产品设计的主要约束。使用路径查找工具,封装和 PCB 设计师能协作找到物理设计约束内的最佳封装,并可简化复杂封装的扇出和布线。

对于每种设计,可以在 PCB 上进行传统布线,以决定最佳的封装和管脚输出。规则允许设计师定义各种参数,如未使用的输出拐角管脚,让差分对连在一起,分配电源和接地的方法,以及处理数据和地址总线的方法等。

一旦确定规则,就不只是“按下按钮再坐回去”,而是比使用电子表格和管脚列表更加直接、更加快速、更加准确,这就是现状。

优点

工具认知设计具有显著的优点,并且其能够在任何设计领域中进行设计优化。首先,其能更加容易地定制多个封装设计,以便按照所需的外形参数最佳地利用给定的元器件。然后从多个“假设分析”情境审视设计,如更小的封装、更少的成本、最简单的扇出和出口等。其次,由于存在大量管脚,利用电子表格和管脚列表进行封装设计就显得力不从心。当人工输入数以百计的管脚数据时,错误率几乎为 100%。当然,其优点还包括:质量的提高、获得适合外形参数的最佳封装、错误的减少以及在整个系统设计中节省大量的时间。

评论