用低成本FPGA实现Femtocell基带架构

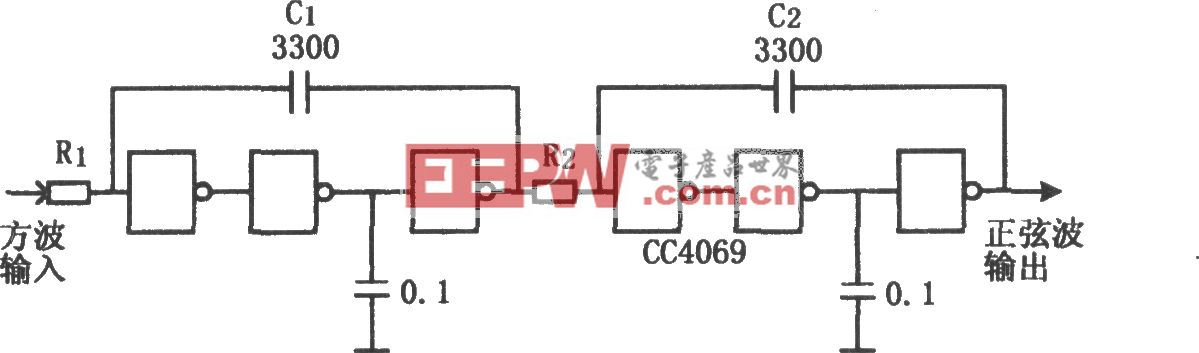

过去的25年里,FPGA在无线基础设施的开发和部署中扮演了重要的角色。无线设备市场跨越了大批量FPGA生产与小批量ASIC生产之间的沟壑。基站成了历史的分界点,因为基站的升级和大规模部署所需器件量可达数万乃至数十万(图1)。

低成本毫微微蜂窝(Femtocell)的出现以及它们所具有的数百万单元的预期潜能使得外界观察者可能得出这样的结论,FPGA已最终在这一应用领域得到了发展。本文主要分析Femtocell的架构,阐明创新的FPGA结构如何在新兴的Femtocell中起到重要的作用。

Femtocell的架构

Femtocell是适合于家庭的小型基站,可支持单个家庭或少量用户。人们正在构想各种各样的Femtocell部署方案,范围覆盖农村、城市及郊区,这些基站仍被看作接入点基站(APBS)。Femtocell正在逐步成为无线基础设施扩展的最终媒介,其原因如下:它们支持现有的3G手机;根据本地需求扩展无线网络容量;CAPEX成本转移至消费者;消费者把他们的Femtocell与家中的有线(电缆或光纤)连接,解决了回传瓶颈问题。

图1:Femtocel技术。

用简化的定义,很显然,Femtocell基站必须具有与传统基站同样水准的功能特性。此外,家庭被认为是Femtocell理想的部署场所,因为这样可以发挥出其增值特性,例如真正高质量的语音、更快的数据和音乐下载中心,以及家庭内部通信系统等。置于家中的基站还具有巨大的潜能,广告商通过它可以向用户家庭提供具有高度针对性的信息。所有这些因素都强调需要构建灵活的Femtocell,特别是在最初的实施阶段。

简化的Femtocell

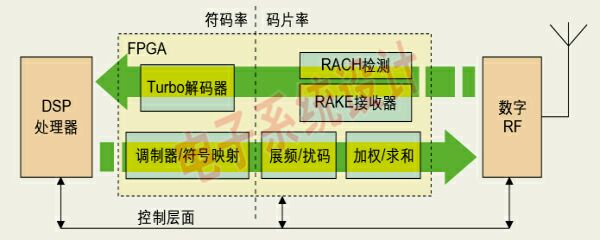

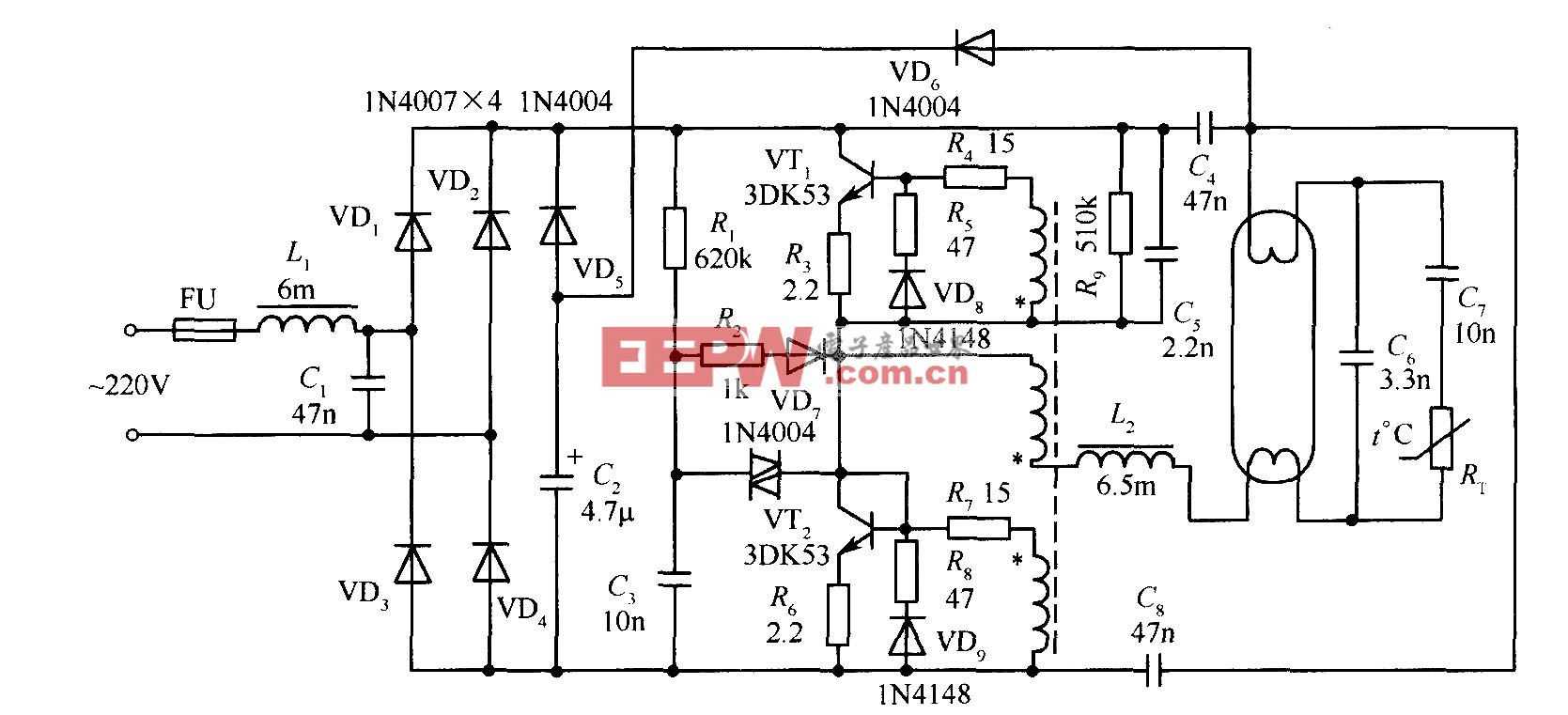

家庭环境确实简化了Femtocell的一些特性需求,这为在器件级实现这些特性增加了一些选择。首先,Femtocell只用于支持少量用户,这大大减少了整个系统的处理需求;第二,它不像传统基站需要支持快速行驶车辆上的终端用户,Femtocell只需要支持居家范围内行走的用户,这大大简化了用于寻找和支持他们的搜索算法。这两个主要差别使得仅用为数不多的几个芯片就能实现一个Femtocell基站(见图2)。

图2:简化的Femtocell框图。

深入探讨Femtocell

通过更深入地探讨这一新的令人兴奋的部署方案,可以迅速地揭示其复杂性,并了解为什么FPGA对其成功至关重要。首先要弄清楚的是,用户采用的是哪种回传技术(FTTx、Ethernet、ATM、DSL等),以及这些回传技术对Femtocell设计有何影响。第二,需要支持什么样的空中接口?尽管这里所讨论的主要是针对WCDMA/HSPA和CDMA/EV-DO,不过也需要考虑支持目前广泛应用的GSM技术。如果WiMax和Wi-Fi Femtocell设计获得成功,还需要支持这些标准吗?同时,在家中安装这种基站还存在一些需要解决的问题,如安全性、访问控制、宏单元的冲突,递交与分发。所有这些问题都再次表明,需要构建灵活的Femtocell架构。

Femtocell的成本压力

要在每个家庭普及这种Femtocell基站必然要面临成本最小化的压力。目标价格为100~200美元的Femtocell基站正处于论证中,这一价格区间远低于当今具有完备特性的旗舰级FPGA的成本。

幸运的是,这一相对较新的基站架构出现之时,正是低成本FPGA普及程度得到迅速发展的阶段,已经占据整个市场的大约25%。FPGA供应商已开发出拥有嵌入式特性的低成本FPGA,例如DSP块、嵌入式存储器和高速SERDES,只需要高端FPGA的一小部分成本便可实现无线基带处理的性能需求。

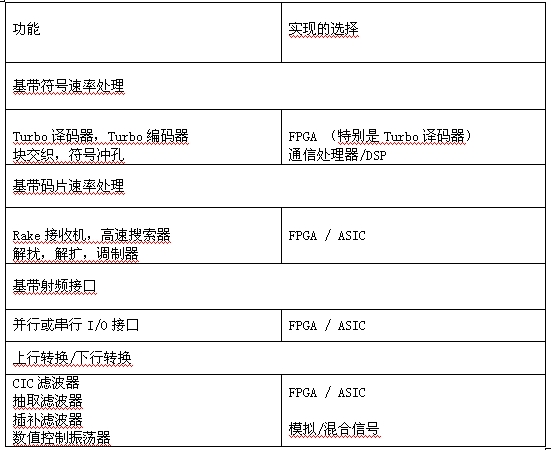

传统的DSP/FPGA处理

多年来在无线应用方面,FPGA和DSP是协处理伙伴。随着低成本、性能丰富的FPGA和专用于无线应用开发的处理器的出现,对预期的大批量Femtocell应用,这个协作关系仍然成立。这些经过相应简化的处理器可支持小型基站相应比较少的功能需求,与高集成度的处理器相比,这些处理器大大减少了成本。表所示是处理器和FPGA之间的一些性能差异。

处理器和FPGA之间的一些性能差异。

在构建传统无线基础设施时,表中所述的许多功能从FPGA和通信处理器移到ASIC,这种做法延续了多年,在最初实施的时候没有ASIC是十分普遍的现象。预期Femtocell的早期部署将会遵循相同的历史路径。因此,前面所述的若干ASIC的功能将用低成本FPGA或者专门的通信处理器实现。

例如,基带码片率处理可以进行分割,以至于RAKE接收机、RACH检测器、展频、加扰和通道加权/求和功能可以全部从处理器转移到用硬件来实现。此外,针对硬件加速,像turbo解码、调制和符号映射等码片率处理功能也是可选的。像LatticeECP2M系列FPGA器件使得这种基于硬件的解决方案在单片、高集成度、低成本器件中得以实现,这使得提供具有嵌入式DSP、存储块和高速串行接口等多种传统的高端功能成为可能,而在价格方面,可以使系统设计者跟上Femtocell市场的价格变化。

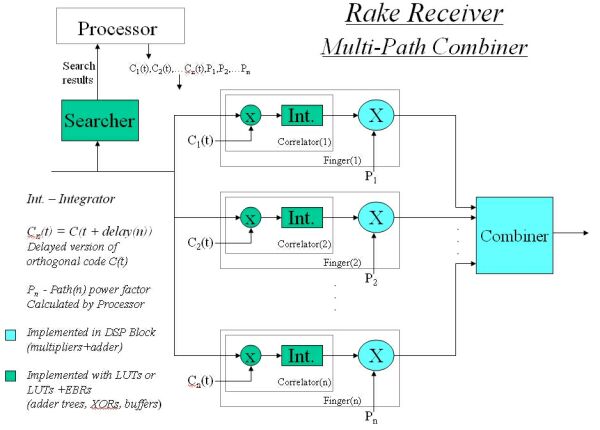

基带实现实例:RAKE接收机

在优化无线通信信号接收质量过程中,PAKE接收机是一个很关键的因素,特别是当它与W-CDMA/UMTS相关时。在室外环境,必须处理多径干扰和衰减,RAKE中需要增加更多的耙指,通过更复杂的Rx电路来保证通话质量。相比之下,对于Femtocell来说,居家环境中比较确定的移动性意味着可以简化掉这些需求。那么,在实现这些特性时在器件层面产生了多个选择。可以考虑的多个架构选项之一是减少RAKE接收机中所需耙指的数量,这样简化了设计,更重要的成本会更低。关于在给定的Femtocell环境中,有关耙指数量的讨论正在进行中,这进一步强调了灵活、低成本的硬件实现方案的重要性。

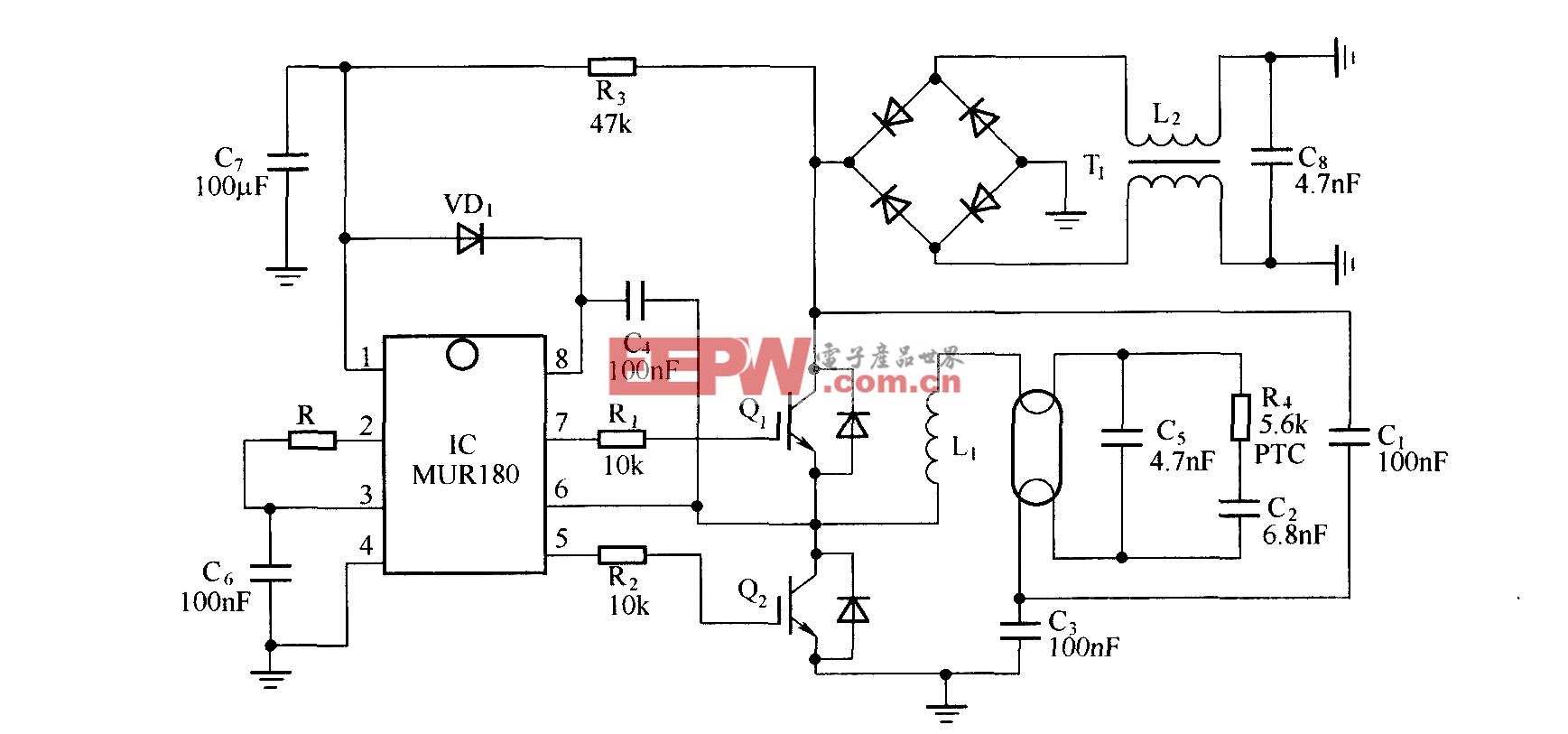

最大速率组合(MRC)是一个普通的RAKE接收机实现方案,它聚集了来自不同路径的信号能量。这个信息用于决定应该分配给特定用户的耙指数量,并用于计算初始延迟或耙指偏移。每个耙指作为一个相关器,加权,乘以耙指输出,然后组合为MRC输出。MRC功能及其在FPGA中的实现方案如图3所示。

图3:RAKE接收机结构的实例。

可编程技术的优势

主要无线基础设施供应商很清楚ASIC、单片ASSP和FPGA各自的优点。对于包含一些新兴规范的应用,或者需要定制逻辑时,可编程性对设计者来说是必需的。可编程性帮助系统设计人员设计出可以混合供应商的特殊逻辑并能提供多区域解决方案的单个硬件平台。

作为支持主流无线手持设备的小型基站,Femtocell需要支持3G及其它版本(HSDPA/自适应天线/MUD/PA线性化),以及4G技术。此外,Femtocell将增加一些可发挥居家环境优势的独特的增值特性,对世界上某些区域,其中一些特性是特定的,仍需做出定义。

当基于有线和无线网络的CPE汇聚于相邻的Femtocell时,还应明白以太网在Femtocell回传中扮演了重要的角色。因此,选择FPGA时的一个重要考虑是要具有片上嵌入式高速以太网接口。

最重要的是,运营商已声称Femtocell要获得成功一定要满足特定的成本目标。低成本FPGA现在能提供Femtocell必需的SERDES、可编程逻辑和DSP功能,并能达到先前高端FPGA或ASSP/FPGA组合未能达到价格水平。这些低成本的FPGA兼具DSP块、嵌入式存储器和SERDES等嵌入式特性与可编程逻辑,这些新型低成本器件与专门的处理器相结合,对实现Femtocell来说是一个颇具吸引力的解决方案。

本文小结

随着技术的发展,无线设备供应商依赖FPGA实现了多种功能。在这激动人心的发展过程中,Femtocell代表了又一个台阶,它也是无线技术革命的又一实例,在其最初的实施阶段充分利用了当今低成本FPGA所提供的灵活性。这些优点包括快速的产品上市时间,在不修改硬件的情况下适应规范的改变,灵活实现各种特性并将多种功能集成到一块芯片上,同时其成本仍支持大批量、低成本的实施。

评论