100进制计数器

定义集成计数器的高低位,1#芯片为低位(相当于个位);2#芯片为高位,(相当于十位),从低位开始计数,把计数脉冲CP送入1#(低位)集成计数器的CP端。B.寻找进位信号,进位端C发出的就是进位信号,这是从0~9的计数过程中,计数到Q3Q2Q1Q0=1001(9)时,发出的高电平信号。C.74LS160是CP上升沿有效的集成计数器,高位芯片需要一个脉冲上升沿进行触发计数,并且,就进位的时机而言,应该在低位芯片的状态是9à0(Q3Q2Q1Q0=1001à0000)时刻,此时,进位输出端C:从1à0,这是一个下降沿,这也是我们需要的进位信号,只是信号边沿不对。可以用一个非门进行信号边沿的转换,把下降沿变成上升沿。低位计数器的C端通过一个非门连接到高位CP端,完成十进制到100进制的级联扩展。

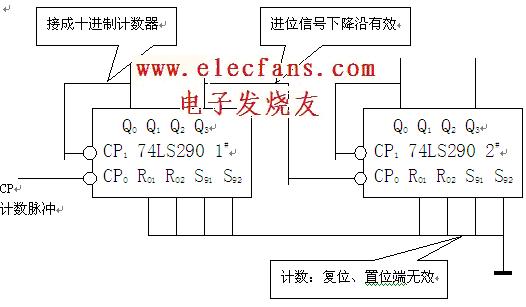

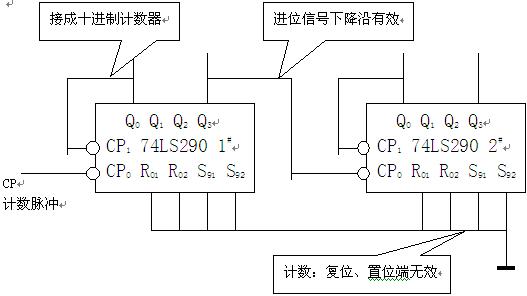

有些集成计数器没有进位端C,这又怎样进行级联扩展呢?例如:使用两片二-五-十进制计数器74LS290组成100进制计数器。

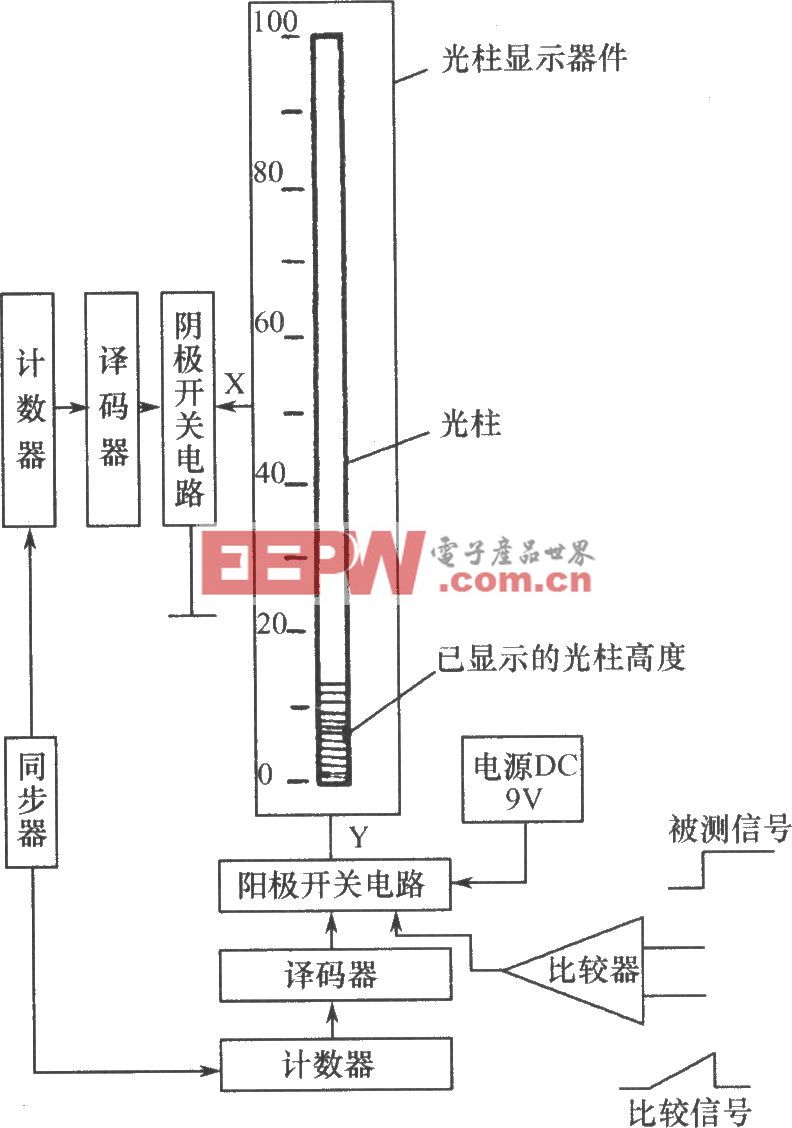

图3-2 异步级联法组成的100进制计数器(2)

A 定义1#芯片为低位,2#芯片为高位

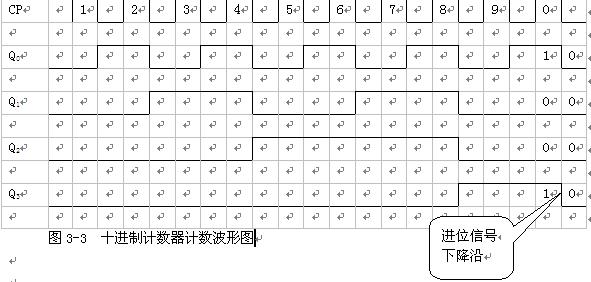

B 通过对一个计数周期的波形图的观察、分析,确定进位信号。

从图3-3中,我们可以发现,74LS290是CP下降沿有效的计数器,Q3在一个计数周期中,0à1à0的变化只有一次,满足进位信号的要求,可以作为进位信号。在什么时刻发出进位信号呢?应该在第10个脉冲下降沿,低位计数器完成一个计数循环,低位计数器从9归0(Q3Q2Q1Q0=1001à0000)的这一时刻,此时,Q3从1到0产生一个下降沿这个下降沿符合进位信号的要求,也符合人们的计数习惯,又满足74LS290计数器CPa触发有效的需要。可以认为,低位集成计数器中二进制数表示的最高位Q3的下降沿能够作为进位信号。

用低位集成计数器Q3直接连接高位集成计数器的CP端。

总之,级联扩展的关键在于,从低位计数器的输出端寻找一个能够代表低位计数器完成一个计数循环的进位信号,并选择恰当的时机送到高位计数器作为高位计数脉冲。通过这两例,我们可以看出,进位信号C、二进制数或代码最高位输出端Q3都可以作为进位信号。在连接时,一定要注意集成计数器的有效边沿。进位信号提供的“进位信号边沿”应与高位集成计数器CP有效边沿一致,否则,应加非门反相。

用以上两种方法级联扩展组成的计数器,是用低位集成计数器的进位信号去触发高位集成计数器的CP脉冲端,各集成计数器没有共用CP脉冲,称之为异步级联。这种级联方式的过度干扰大,不适合于要求过度干扰小的计数器。怎样克服这种过度干扰呢?可以用同步级联法组成同步计数器来克服过度干扰。所谓同步计数器就是:所有的集成计数器及其内部的触发器共用同一个CP脉冲的计数器。

评论