基于SMS4的加密通信可编程片上系统设计实现

摘要 针对面向工业用、商用以及民用电子设备加密串行通信需求,通过基于SMS4的加密通信SOPC软硬件架构、SMSd加密通信控制器IP技术、SMS4加密通信软件技术等内容的研究,实现了基于SMS4加密算法的串行通信技术,并在非128位明文的加密传输数据控制和基于8位异步模式的128位数据串行收发上效率明显提升。基于SMS4的加密通信SOPC提高了系统的加密通信功能可定制能力,且使加密通信核心算法自主可控。

本文引用地址:https://www.eepw.com.cn/article/201610/306411.htm串行通信是商用、民用及工业控制用电子系统广泛使用的一种通信方式,多种电子系统通过串行通信接口传输敏感数据,如无线电通信设备、IC卡刷卡机等,为保证数据传输安全,对串行通信数据加密是必要的技术手段。SOPC技术是百万门级大规模FPGA出现后新兴的电子系统设计技术,实现的电子系统具备集成度高、功能可配置、性能可伸缩和资源可重构的特点。因此,采用SOPC技术设计加密通信系统具备良好的应用推广价值。

分组密码算法是大量数据加密存储与传输的主要密码算法,SMS4算法是我国官方公布的第一个商用分组对称密码算法,为发展自主可控的信息安全技术,应该将SMS4算法作为串行通信核心密码算法的重要选择。由于SMS4算法提出较晚,目前尚未有采用SMS4算法进行加密通信SOPC设计的成果出现。为使信息安全技术自主可控,优化加密通信系统设计,提高系统的加密通信功能可定制能力,因此有必要开展基于SMS4的加密通信SOPC研究与设计。

分组密码算法具有速度快、易于标准化和便于软硬件实现等特点,通常是信息网络安全中实现数据加解密的核心体制,其在计算机通信和信息系统安全领域有着广泛的应用,如国外发布的DES算法、AES算法、NESSIE算法等。2006年1月,我国国家商用密码管理办公室公布了SMS4分组密码算法标准,用于保护无线局域网产品的数据安全,并被WAPI标准采纳作为其中的分组密码算法。2007年12月,在国家密码管理局公布的《可信计算密码支撑平台功能与接口规范》中,SMS4算法被规定为可信密码模块(TCM)中要求实现的对称密码算法。

SMS4是一个分组对称密码算法,分组长度和密钥长度为128 bit。加密算法与密钥扩展算法均采用32轮非线性迭代结构。其中非线性变换所使用的S盒是一个具有很好密码学特性的、由8 bit输入产生8 bit输出的置换。但不存在永远安全的密码算法。SMS4设计灵活,其中所采用的S盒可灵活地被替换,以应对突发性的安全威胁。

1 基于SMS4的加密通信原理

SMS4密码算法是一种128位数据输入输出的加解密算法,输入数据需经过32轮的函数运算才能得到输出结果,存在较大的首个数据输出潜伏延迟,而一旦进入连续输出,通过硬件流水线设计可达到较高的吞吐率。串行通信控制器是一种典型的中低速通信设备,由于受到串/并转换、波特率除数分频、16分频收发等设计的影响,串行通信速率不可能有较大提升。因此,SMS4算法和串行通信之间存在明显的吞吐量不匹配问题。

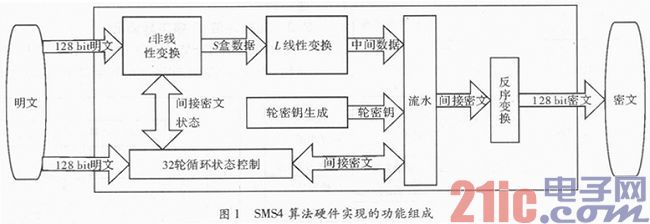

通过研究SMS4密码算法32轮迭代运算、轮密钥运算的运算特点,并分析全流水、全循环、循环与流水结合、单引擎、多引擎等硬件运算结构,提出合适的运算结构作为算法的基础实现结构,以轮函数内部分级流水、节拍同步作为进一步优化的手段,突破面向串行通信的SMS4算法硬件实现优化技术,使该算法逻辑占用较少的FPGA内部资源,并使其算法的运算速度能尽量接近串行通信速率,最终达到资源占用与运

算性能的平衡。该算法硬件实现的功能组成如图1所示。

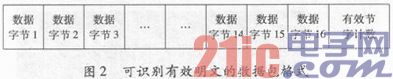

串行通信过程中,最小的数据收发单元为8位数据,即1 Byte。对128位SMS4加密运算而言,输入的明文数据可能不是128位数据,而是1~7 Byte,无法直接完成明文的SMS4加密运算。在128位密文发送过程中,若对应明文不是128位的,还需嵌入字节计数值来标识有效数据长度,而字节计数值和有效数据难以区分。在密文接收与SMS4解密过程中,也存在得到字节计数值与有效明文提取的问题。如图2所示。数据包具备16 Byte的数据段和1 Byte的有效字节计数值,通过有效字节计数值识别数据段中的有效数据,而其他数据则为填充数据。

通过分析处理器访问8位通信控制器的特点,采取有效硬件逻辑设计延长8位明文连续写入等待时间,尽可能具备128位明文输入。通过字节自动填充将非128位明文输入补满到128位,实现明文的128位SMS4加密运算。将有效数据/字节计数值混合编码,实现非128位明文对应密文的发送、接收、解密与填充字节去除。通过以上技术手段,突破非128位明文的加密传输数据控制技术,使处理器始终按8位明文数据访问SMS4加密通信控制器,屏蔽128位加解密过程,具备非128位明文的加密传输数据控制过程对处理器透明、兼容通用串行传输协议、处理器加密通信负载小等特点。

一般的串行通信控制器以8位数据进行收发,当进行128位密文传输时,存在数据发送接口、数据接收接口、接收线状态接口设计的位宽不匹配问题。通过设计128位宽发送数据FIFO、128位宽接收数据FIFO、128位区间接收线状态FIFO,缓冲128位密文数据和相应的接收线状态;通过128位/8位收发匹配逻辑,实现发送数据的128位/8位转换、接收数据的8位/128位转换、连续16 Byte的接收线状态组合译码;通过以上技术手段,突破基于8位异步模式的128位数据串行收发技术,使128位密文串行收发无需软件干预,故进一步降低了处理器的通信接口处理负载。

2 基于SMS4的加密通信实现

2.1 SMS4加密通信控制器IP技术

SMS4加密通信控制器IP功能组成如图3所示,分为8位串行收发功能逻辑、128位收发逻辑、面向串行通信的SMS4算法逻辑、非128位明文的加密传输数据控制逻辑和处理器访问接口逻辑。SMS4加密通信控制器IP对外提供8位数据位宽的处理器访问接口和8位串行收发数据接口,并兼容通用串行传输协议,将128位SMS4密码运算隐藏在IP内部。

8位串行收发功能逻辑提供8位数据收发、接收线状态检测、MODEM线控制与线状态检测功能。128位收发逻辑使128位SMS4密文和8位串行收发数据之间的传输能够平滑、顺畅地进行。面向串行通信的SMS4算法逻辑在完成128位SMS4加解密运算的同时,还具备FPGA资源利用少、加解密吞吐量与串行通信吞吐量匹配的特点。非128位明文的加密传输数据控制逻辑重点解决非128位明文的加解密运算和串行传输问题。处理器访问接口逻辑为处理器提供8位数据位宽的访问接口,使处理器对SMS4加密通信控制器IP的访问方式尽可能地接近于一般的8位串行通信控制器。

2.2 加密通信IP核仿真验证

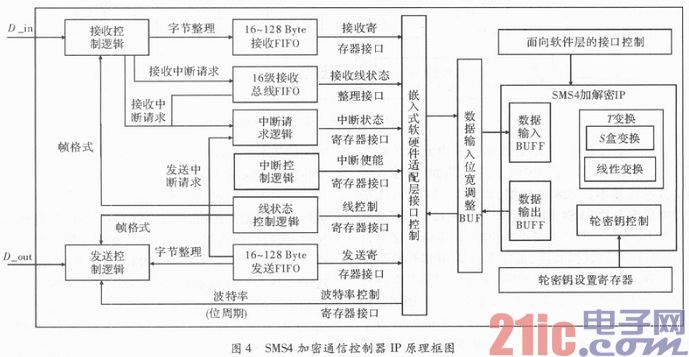

本文设计了SMS4加密通信控制器IP核完成加密通信,图4为SMS4加密通信控制器IP的原理框图。

采用Altera公司的Quartus II FPGA开发工具完成SMS4加密通信控制器IP的HDL代码编译。

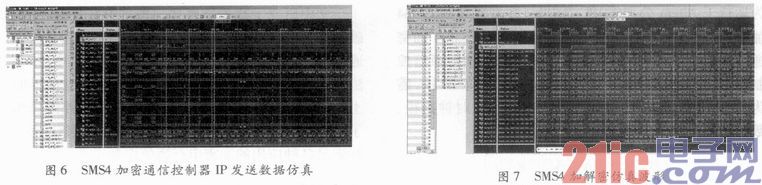

使用ISim仿真器进行SMS4加密通信控制器数据接收与发送仿真,得到仿真波形,如图5和图6所示。SMS4加密通信控制器IP对加密算法、数据收发、数据缓冲、接收线状态等功能进行了模块化设计,各个模块既相对独立又有机组合,可完成各自功能,不同模块之间进行数据和信号的交换实现时序控制、信息交互,从仿真结果可看出,SMS4加密通信控制器IP在不影响通信吞吐量的情况下,实现了数据的SMS4的加解密处理。

如图5所示,SMS4加密通信控制器IP接收数据通过信号wb_cyc_i作为计数器,每接收一个有效数据,产生一次脉冲。we_sel_i表示接收控制器片选信号,在接收期间保持为高;wb_adr_i表示数据地址,wb_dat_i则表示接收数据值。

如图6所示,SMS4加密通信控制器IP接收数据通过信号wb_cyc_i作为计数器,每接收一个有效数据,产生一次脉冲;we_sel_is表示发送控制器片选信号,在发送数据期间保持为低。wb_adr_i表示数据地址,wb_dat_i表示接收数据值。

面向串行通信的SMS4算法逻辑设计,并已集成到SMS4加密通信控制器IP中。使用ISim仿真器对SMS4算法逻辑的Verilog代码进行波形仿真,输入128bit数据,进行加解密,其仿真波形如图7所示。

从图中可看出,SMS4加密IP利用points计算通信量,图7的通信量为1 024bit,data_in表示输入加密数据,addr_wr表示加密过程中的地址转换;data表示输出解密后的密文。

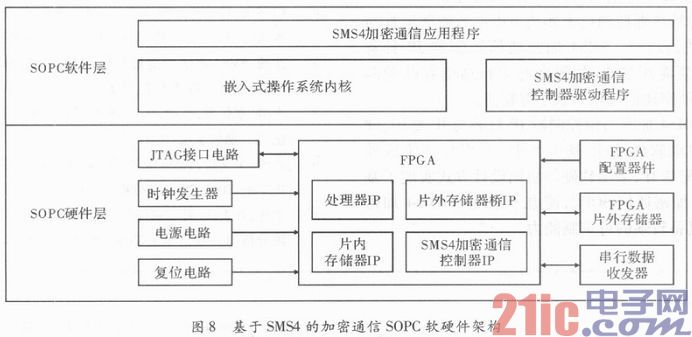

2.3 基于SMS4的加密通信SOPC软硬件架构

基于SMS4的加密通信SOPC软硬件架构如图8所示,分为SOPC硬件层和SOPC软件层。SOPC硬件层由电源、复位、时钟、JTAG接口、FPGA、配置器件、存储器、串行数据收发器等电路组成,其中FPGA是核心器件,内部集成了处理器IP、存储器及桥IP、SMS4加密通信控制器IP等。 SOPC软件层主要南嵌入式操作系统内核、SMS4加密通信控制器驱动程序、SMS4加密通信应用程序等部分组成。

SOPC硬件功能方面,电源电路、复位电路、时钟发生器为SOPC提供必须的电源供应、上电和硬件复位信号、时钟同步信号。JTAG接口电路用于调试SOPC的硬件逻辑和软件程序,同时也用于在线下载FPGA配置文件。FPGA配置器件存储FPGA静态配置,在上电时自动对FPGA进行配置;由于FPGA内部存储资源有限,需外扩RAM、Flash等片外存储器。串行数据收发器实现TTL电气接口信号与RS-232/422电气接口信号的转换,使串行数据收发信号能适应远距离传输环境。

SOPC软件功能方面,嵌入式操作系统内核提供基本的存储管理、设备管理、中断管理及任务调度等功能。SMS4加密通信控制器驱动程序将SMS4加密通信控制器抽象成一个以文件方式访问的设备,供应用程序调用。SMS4加密通信应用程序实现明文数据的收发,由于SMS4加密通信控制器IP可屏蔽密文传输过程,应用程序中无需进行加解密处理。

基于SMS4的加密通信SOPC硬件集成,需软件集成及性能分析。SMS4加密通信SOPC主要依靠专用串行接口扩展模块的FPGA芯片进行硬件集成,图9为运行于Altera公司SOPC Builder开发环境的SMS4加密通信SOPC硬件集成界面。如图所示,SMS4加密通信SOPC集成有NiosII处理器IP、SMS4加密通信控制器IP、SRAM和Flash的存储器控制IP等IP核,需为各IP核指定Avalon总线互连拓扑关系、时钟路径、数据访问空间及中断路由等。

3 结束语

面向串行通信优化SMS4算法的硬件实现,通过基于8位异步模式的128位数据串行收发技术实现SMS4加解密和串行通信的深度整合,通过非128位明文的加密传输数据控制技术实现SMS4加解密运算与处理器无关,设计的SMS4加密通信控制器IP具备FPGA逻辑资源用量小、加解密与串行通信吞吐量匹配、处理器加密通信处理负载小等特点。

通过SMS4加密通信控制器IP封装与IP复用、硬件抽象层驱动软件设计、基于SOPC开发环境集成处理器IP及配套IP,采用软硬件协同设计方式实现了基于SMS4的加密通信SOPC,使电子系统的SMS4加密通信功能具备较强的可定制能力。

文中研究了基于硬件实现加密串行通信功能,防破解能力强、处理器负载轻,进而提高了应用系统串行通信的安全性,有较好的推广应用价值。其中,核心算法采用SMS4算法,有力支撑了密码学研究成果的本土化,为满足国内信息安全技术的自主可控需求作出了一定贡献。另外,文中设计的可定制SOPC,也可较好满足各种应用的加密串行通信定制需求。

评论