基于ARM的分布式干扰机控制单元设计

在图形界面编程中,多数时候需要对某些“事件”进行处理。例如,当用户点击某个按钮时,应用程序便开始执行某种操作。在Qt开发中,通过一种被称为“信号和槽”的机制来实现对象间的通讯。信号和槽机制,即当一个特定事件发生时,一个或几个被指定的信号就被发射;槽即一个返回值为void的函数,如果存在一个或几个槽和该信号相连接,那么在该信号被发射后,这个(些)槽(函数)就会立刻被执行。

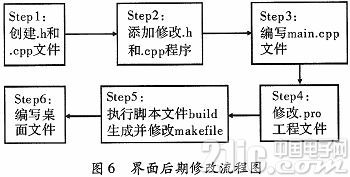

本文引用地址:http://www.eepw.com.cn/article/201609/303796.htm由于设计的控制单元采用大尺寸触摸屏,而触摸屏性能的调试是个重要问题,因为电磁噪声的缘故,触摸屏容易存在点击不准确、抖动等问题。因此一般都要移植一个tslib来配合,在用户层对触摸屏的数据进行滤波和矫正,同时也可给应用程序一个统一接口。tslih能为触摸屏驱动获得的采样提供诸如滤波、去抖、校准等功能,通常作为触摸屏驱动的适配层,为上层的应用提供了一个统一接口。在PC端的界面设计完成后,后期修改流程如图6所示。

经过上述步骤,将编译好的可执行文件拷贝至开发板的opt/Qtopia/bin目录下,将.desktop桌面文件拷贝至opt/Qtopia/apps/Application目录下。重启开发板,就可以在ARM触屏的桌面应用上看到编写的应用程序图标,点击运行就可以初步看到效果。

3 软件功能设计

通过以上工作,可以在ARM开发板上看到整体的界面效果,但要实现该ARM控制单元的功能,还需要在界面程序中添加和修改代码。

3.1 参数设置及数据的发送

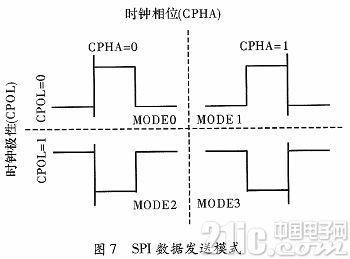

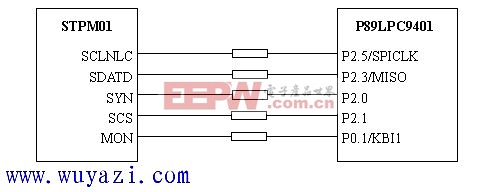

首先对所要发送的数据进行采集并打包。在发送数据之前,还需对已开发成功的SPI做配置。在SPI发送数据时,有4种模式可供选择:(1)CPOL=0,CPHA=0。(2)CPOL=0,CPH A=1。(3)CPOL=1,CPHA=0。(4)CPOL=1,CPHA=1。4种情况分别为MODE0、MODE1、MODE2、MODE3,其中CPOL指时钟信号的极性,表示当时钟信号空闲时,其电平值为低电平0或高电平1。CPOL=0,时钟空闲时为低电平,所以当时钟信号有效时,即为高电平;CPOL=1,时钟空闲时为高电平,所以当时钟信号有效时,即为低电平。CPHA指时钟信号的相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应第一个边沿,1对应第二个边沿。

在本干扰机控制单元通信协议中,是采用模式MODE3。除了要对SPI发送数据的模式设置之外,还要设置SPI模式可写可读、SPI的bit/word可写可读、SPI的波特率可写可读等。将参数设置完成后,按照通信协议的约定,将界面信息对应成相应的数据,每8 bit为一组,每个word共16 bit进行发送即可。

3.2 SD卡存储功能的设计

分布式干扰机在实际使用中,有时需要对设置的某些重要信息进行保存,所以利用Qt中的两个易于合并使用的类:QFile和QDataStrcam。QFile对象表示磁盘上可读取和写入的文件。QFile是代表多种不同设备且应用更广的QIODevice类的子类。QDataStream对象用于按顺序排列二进制数据,以便储存在QIODevice中并供以后检索。读取或写入QIOD evice就如同打开数据流,然后读取或写入一样简单,只是参数为不同的设备。

3.3 定时功能的设计

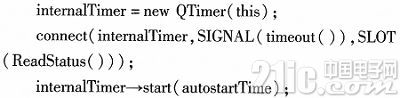

对于实际使用中的干扰机控制单元,需要发送干扰数据时,在界面上进行相应设置,即可直接发送。但是更多时候需要做的是读取并显示干扰机从环境中测到的数据,可以通过点击界面上的更新按钮,但是无法实时更新,所以这里设计一个能够定时自动更新界面信息功能是必要的。定时功能主要利用Qt中的QTimmer类,其核心程序如下:

除此之外,在整个程序中的某些功能函数中,还要加上internalTimer→stop();这行令定时器关闭的代码,原因是在有些界面参数进行设置后或读取并显示后,暂时无需定时读取功能,所以就需关闭定时功能,待需要时再通过internalTimer→start(autostartTime)打开定时器即可。

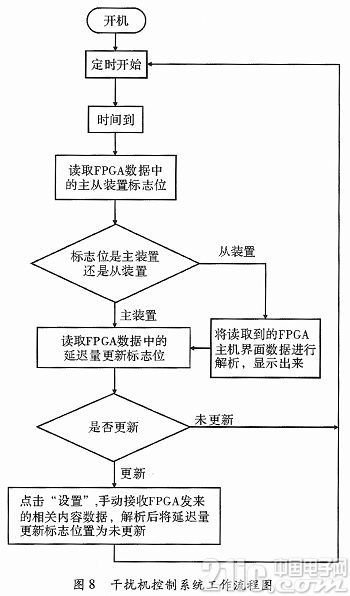

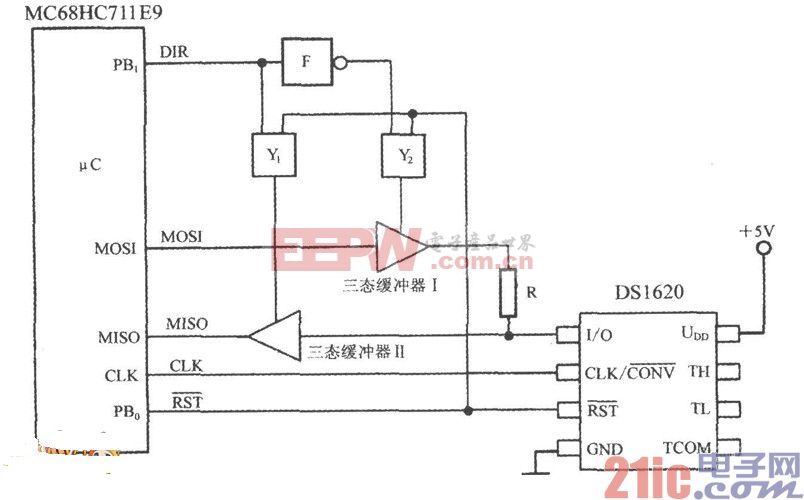

当整个程序的功能全部设计完成后,进行整体测试,流程如图8所示,开机后,ARM会自动启动干扰机控制单元界面,并开始计时。当定时时间到,ARM单元会读取FPGA中的主从装置标志位并进行显示,若读到从机,则将FPGA中的信息显示到界面中;若为主机,直接读取FPGA延迟量更新标志位。若为更新,则表示FPGA有新信息,需要点击设置将当前界面更新为最新参数,然后开始重新计时。

3.4 运行测试

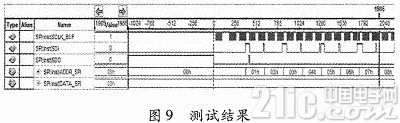

对设计好的分布式干扰机控制单元进行测试,按照与FPGA的通信协议,ARM界面信息转化为数据后,每8位一组,两组为一个信息单元进行传送。反之,当FPGA对ARM发送数据时同理对数据进行解析。利用FPGA的逻辑分析仪对发送与接收的数据进行采样,结果如下图9所示。

图9中,SCLK_BUF为时钟信号,每8个时钟脉冲为一个时钟周期;SDI为ARM发送的数据,SD0为ARM接收的数据;ADDR_SPI与DATA_SPI为ARM发送数据的低8位与高8位。从图中可以看出,ARM端发送的数据依次为00h,00h,01h,00h,02h,00h,03h,00h……。在FPGA一端,收到的数据同样是00h,00h,01h,00h,02h,00h,03h,00h……,其中ADDR_ SPI的数据就是收到数据的奇数项,其中DATA_SPI的数据就是收到数据的偶数项。同时,在第3个有效脉冲周期到达时,ARM控制单元接收到来自FPGA的数据,这个数据解析后反映到ARM界面即为装置属性选项,界面会自动响应将装置属性选项设置为主装置。

评论